# 1717 Interpacing & Digital experiments with your APPLE

**BY CHARLES J. ENGELSHER**

# INTERFACING & DIGITAL EXPERIMENTS WITH YOUR APPLE®

# INTERFACING & DIGITAL EXPERIMENTS WITH YOUR APPLE®

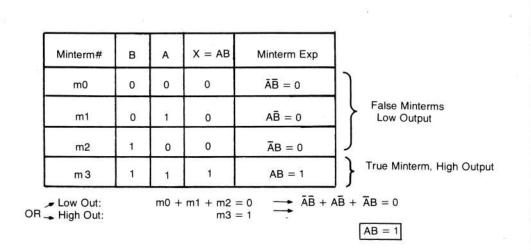

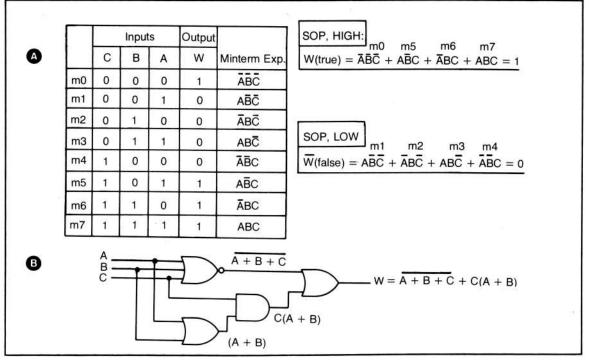

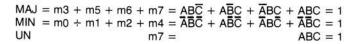

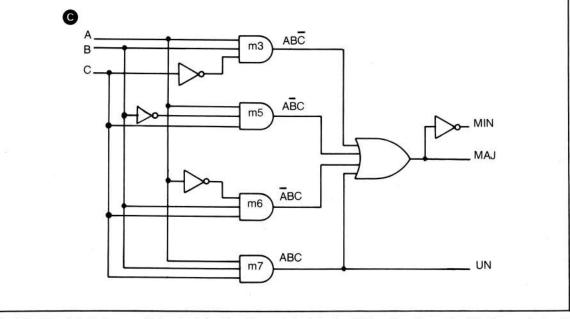

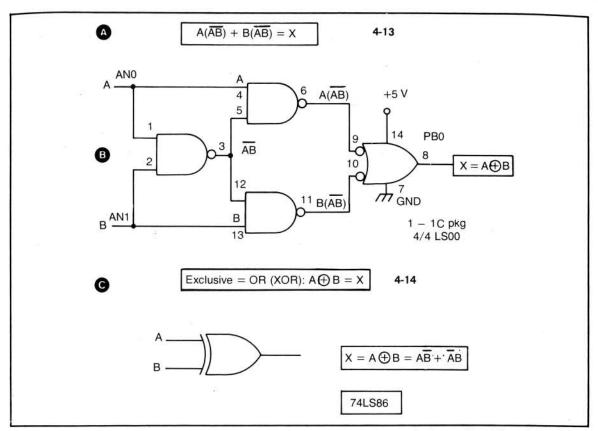

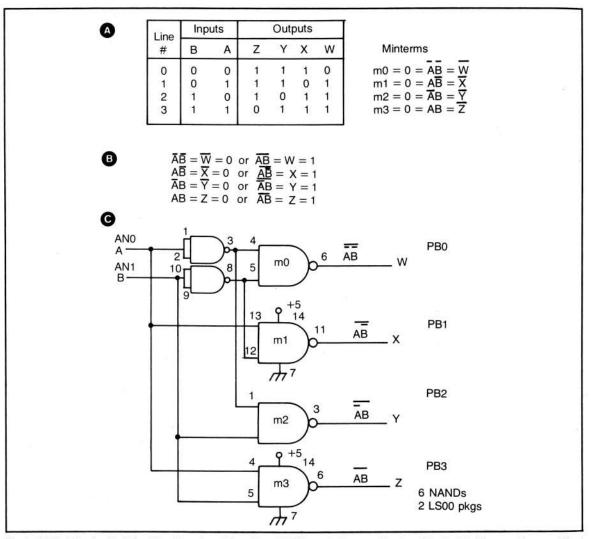

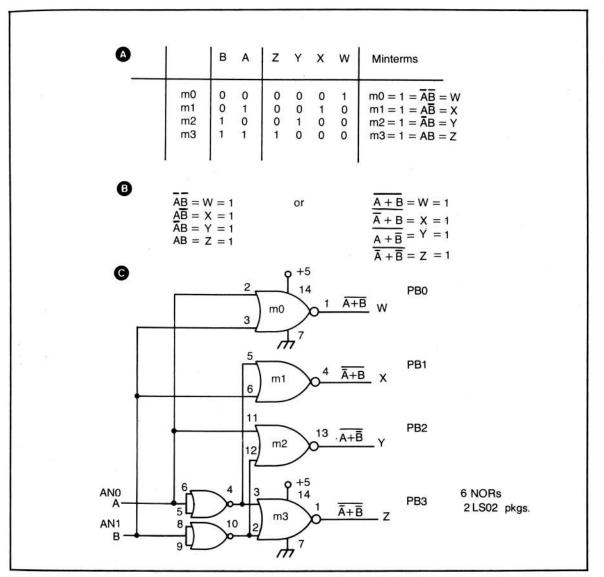

# BY CHARLES L. ENGELSHER

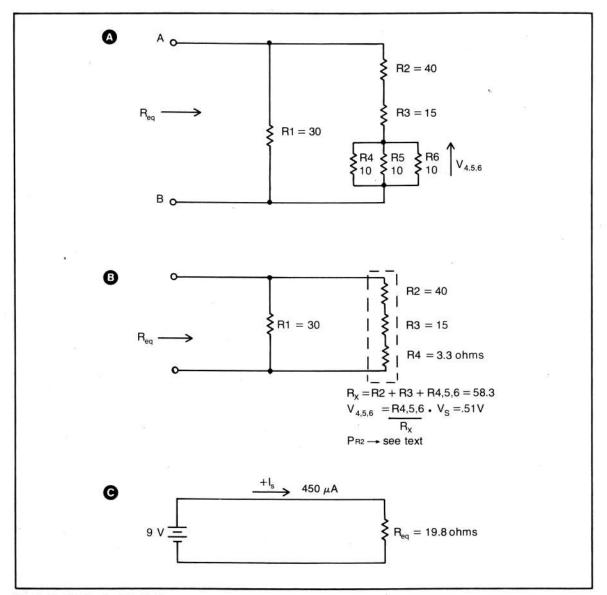

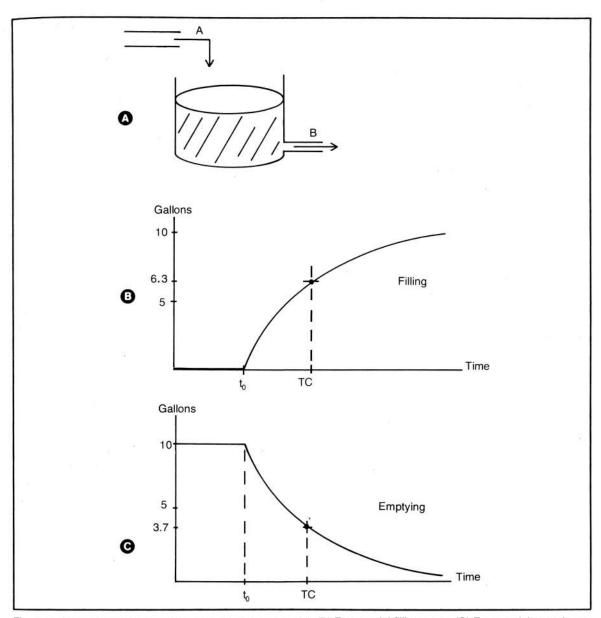

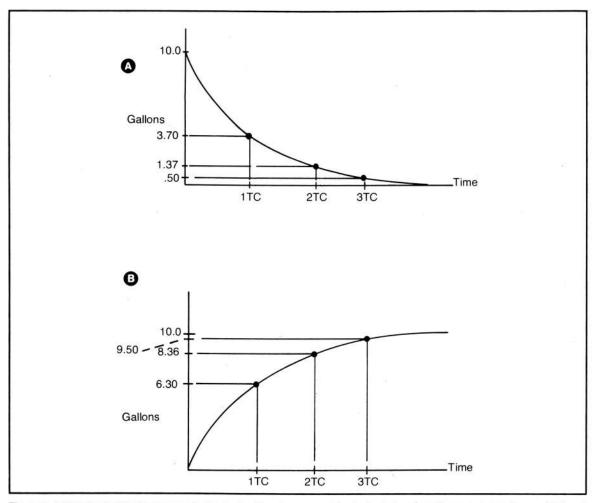

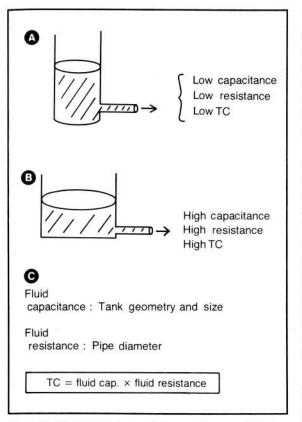

Apple is a registered trademark of Apple Computer, Inc.

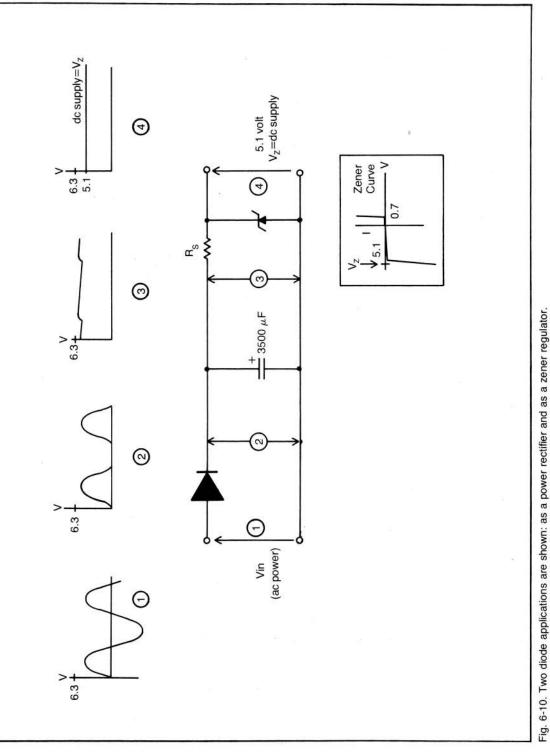

#### **FIRST EDITION**

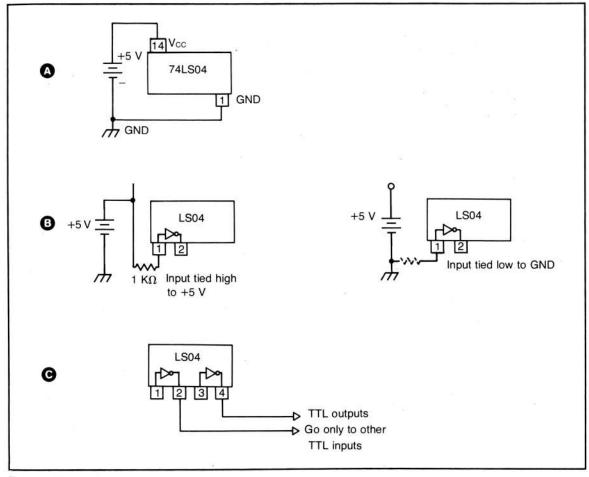

#### FIRST PRINTING

#### Copyright © 1984 by TAB BOOKS Inc.

#### Printed in the United States of America

Reproduction or publication of the content in any manner, without express permission of the publisher, is prohibited. No liability is assumed with respect to the use of the information herein.

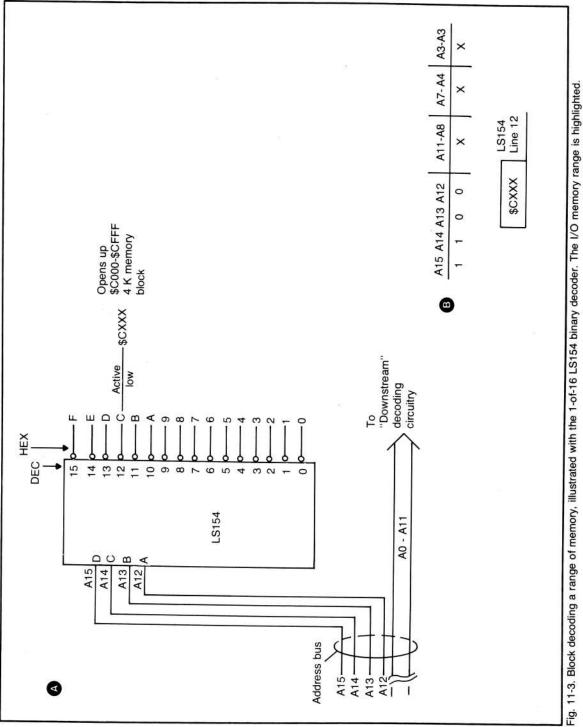

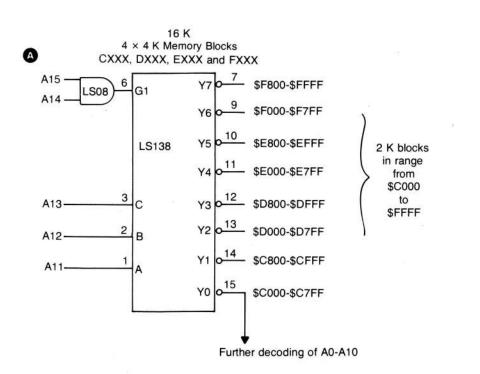

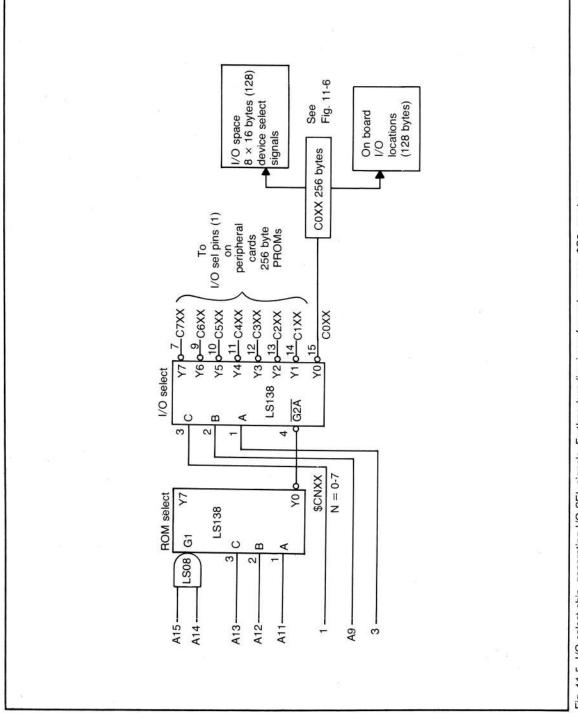

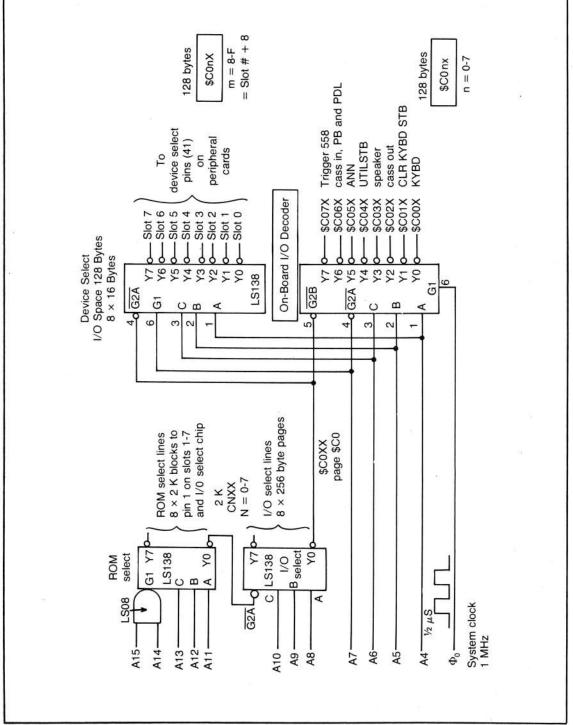

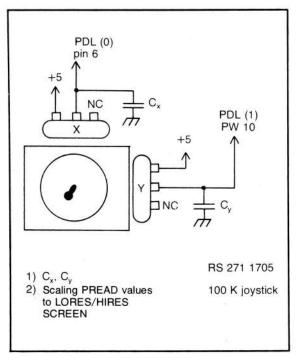

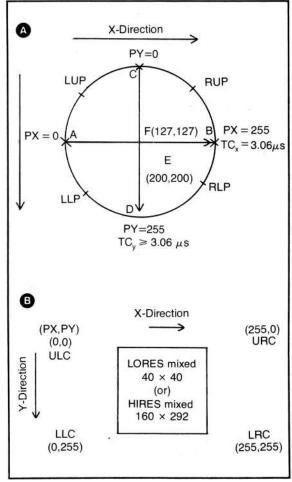

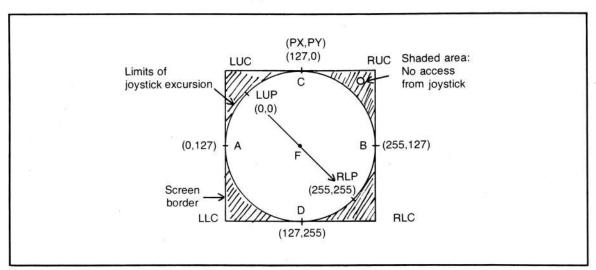

Library of Congress Cataloging in Publication Data

Engelsher, Charles J. Interfacing and digital experiments with your Apple.

Includes index.

1. Computer interfaces. 2. Apple Computer. 3. Digital electronics. 4. Computer input-output equipment.

TK7887.5.E54

I. Title. 1984 621.3819'5835 83-24169 ISBN 0-8306-0717-X ISBN 0-8306-1717-5 (pbk.)

# Contents

|   | Introduction                                                                                                                                                                                                                                                                                             | vii |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1 | Fundamentals of Digital Electronics<br>The Challenge of Digital Electronics—The Microcomputer Solution—Learning about Digital Devices—<br>Digital Devices as Black Boxes—Discrete Components and Device Characteristics—Families and<br>Subfamilies—Scales of Integration—Binary and Hexadecimal Numbers | 1   |

| 2 | The Digital Desktop Laboratory<br>The Game Port Connection—Turning the Apple into a Digital Logic Trainer—The Rest of the Logic<br>Lab—Introduction to the Experiments—Experiment 1, Setup                                                                                                               | 13  |

| 3 | The Six Basic Logic Functions<br>Combinational SSI Devices—Experiment 2, NOT and IS—Experiment 3, AND—Experiment 4, NAND—<br>Experiment 5, OR—Experiment 6, NOR                                                                                                                                          | 37  |

| 4 | Boolean Methods<br>The Rules of Boolean Algebra—Relating Inputs and Outputs—Introduction to the Design Experiments—<br>Experiment 7, SSI Design I—Experiment 8, SSI Design II                                                                                                                            | 61  |

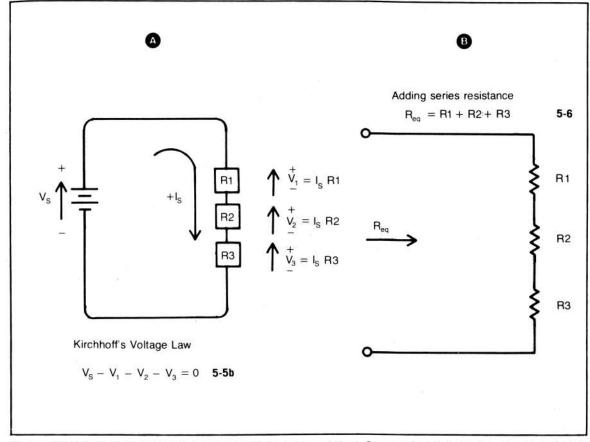

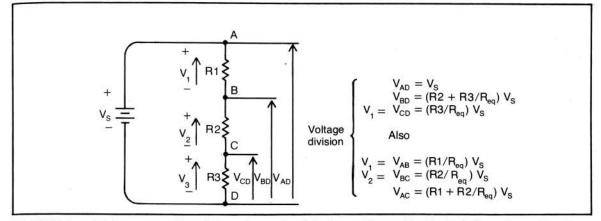

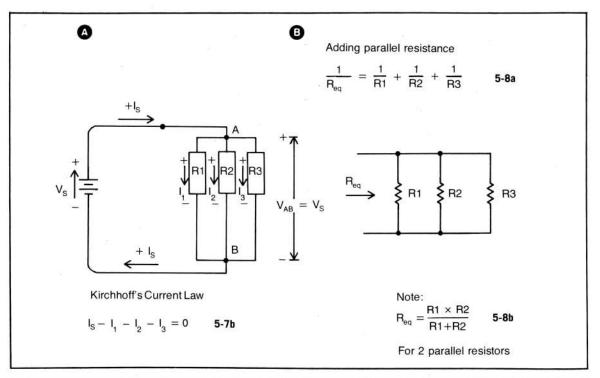

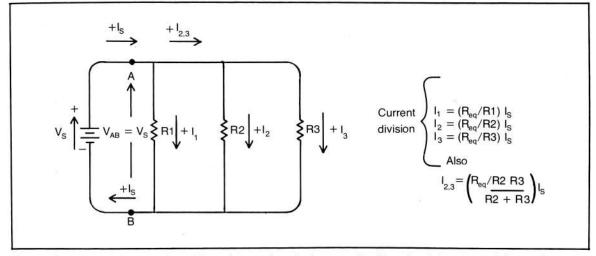

| 5 | Discrete Electronic Components and Laws<br>The Resistor and Associated Laws—Capacitance, Time Constants, and Reactance                                                                                                                                                                                   | 91  |

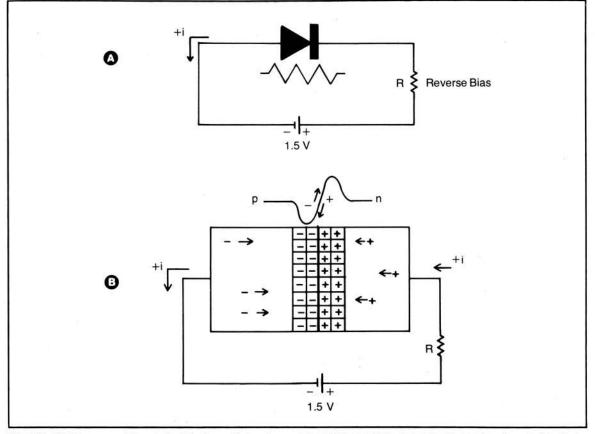

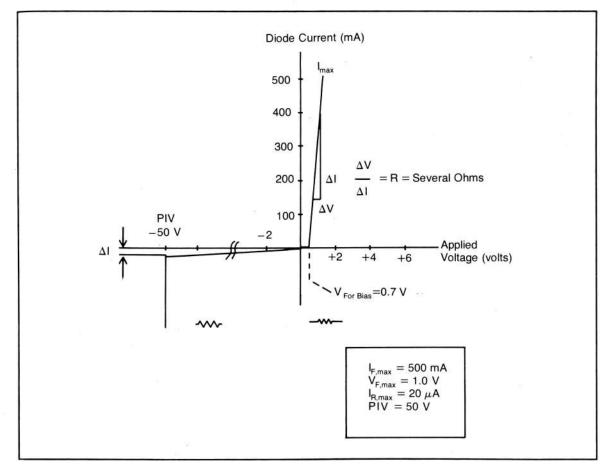

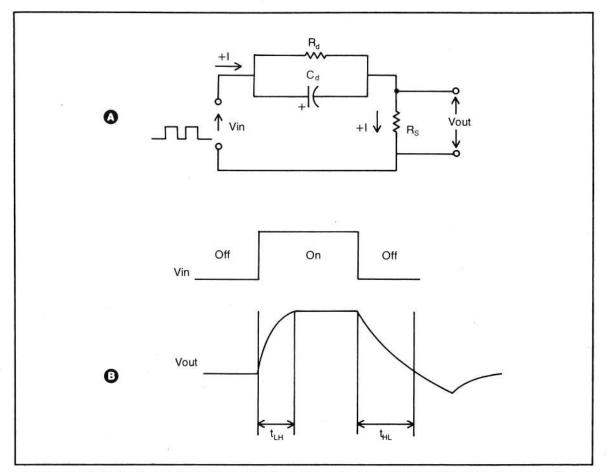

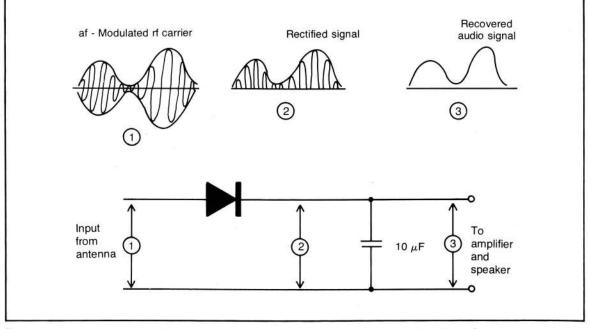

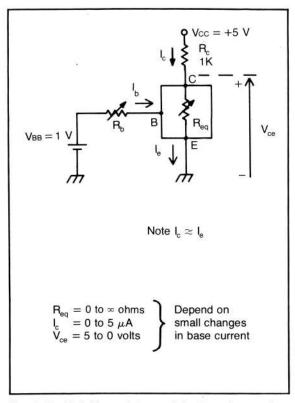

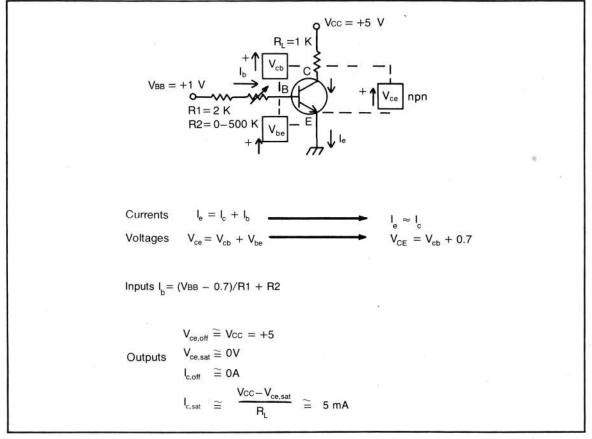

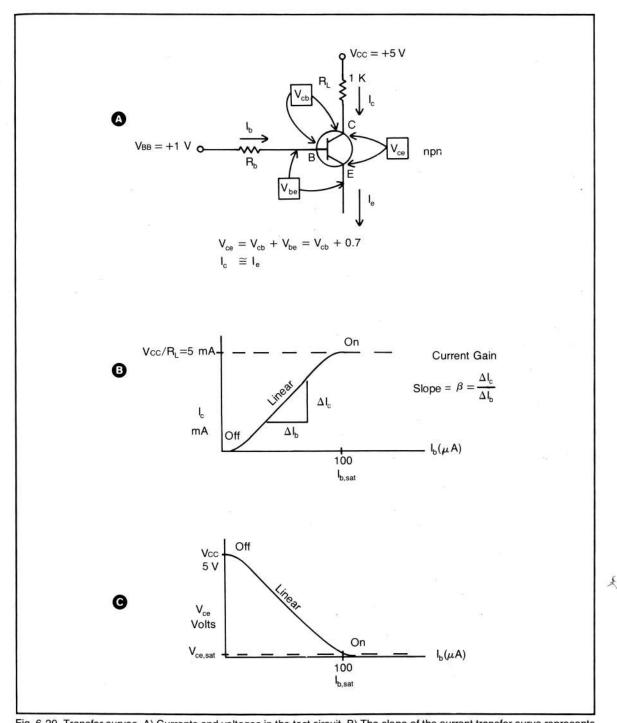

| 6 | The Diode and Transistor<br>Semiconductor Materials—The Diode—The Essentials of Transistor Action—Using the Transistor as a<br>Switch—Experiment 9A, Diode and Transistor Testing—Experiment 9B, Transistor Current Gain and the<br>Overloaded Sink                                                      | 123 |

# 7 TTL Internals

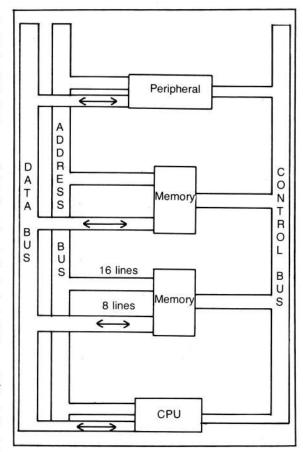

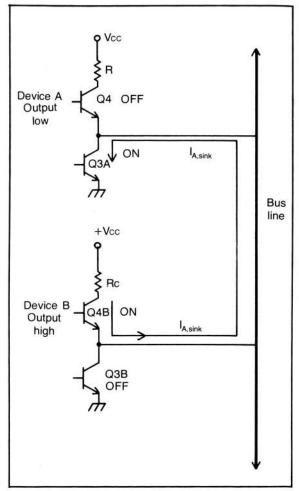

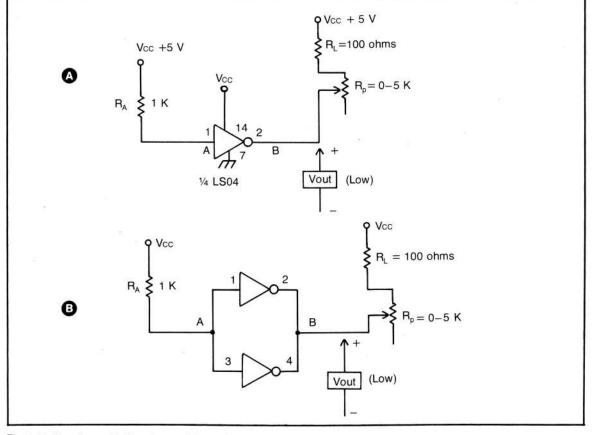

The Electrical Black Box-Inside the Black Box-The Key Parameters of TTL-TTL and Bus Oriented Computer Logic-Experiment 10, LSTTL Sink Current Measurement and Augmentation

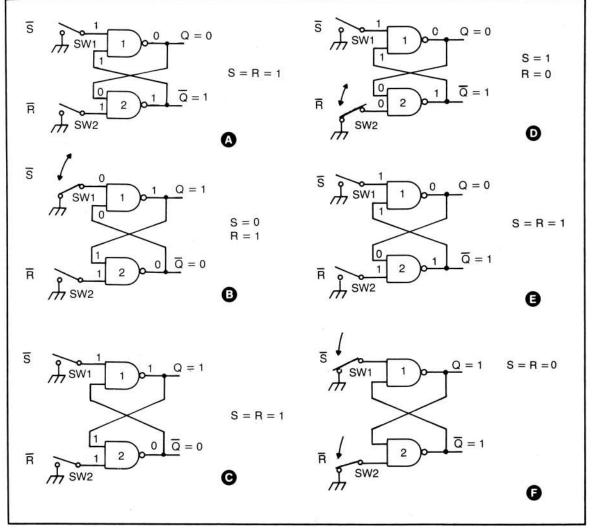

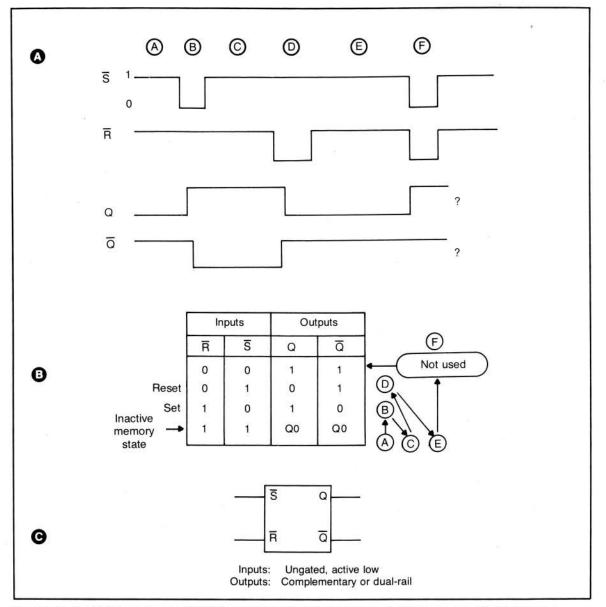

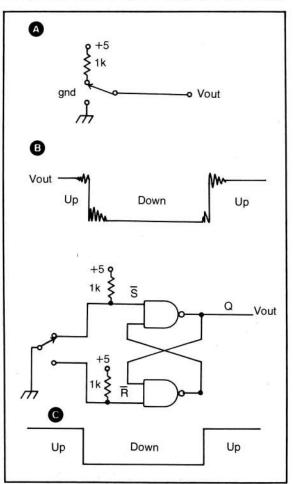

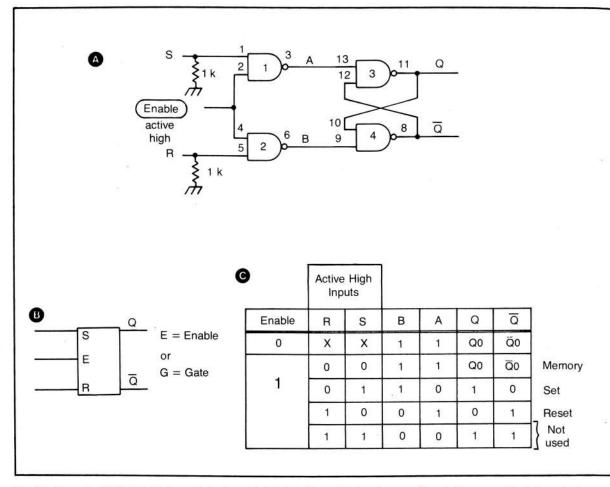

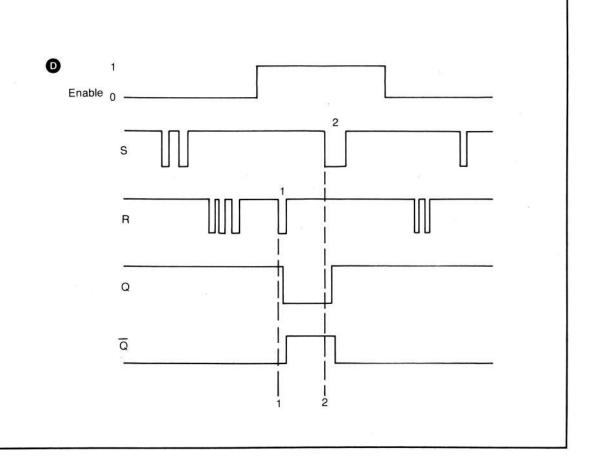

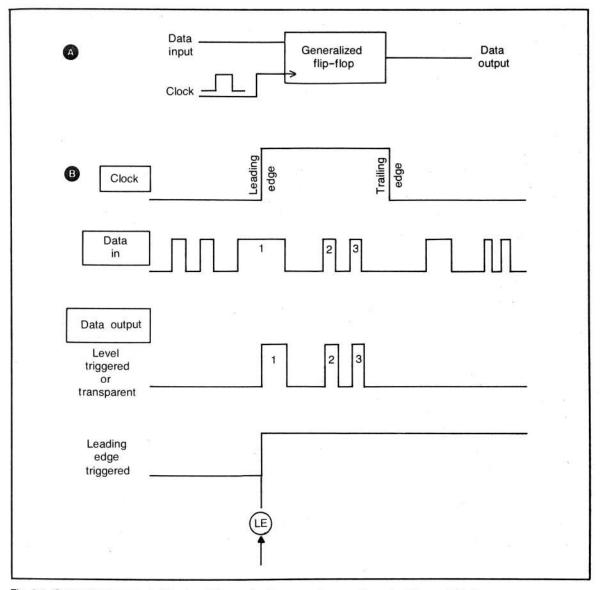

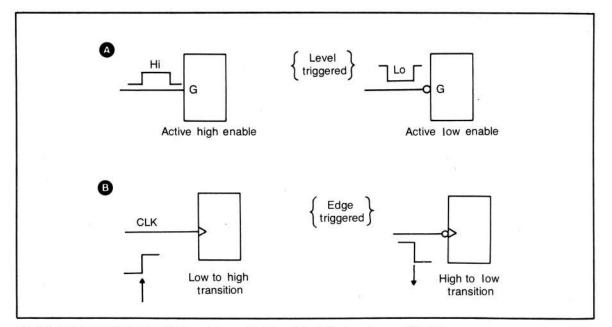

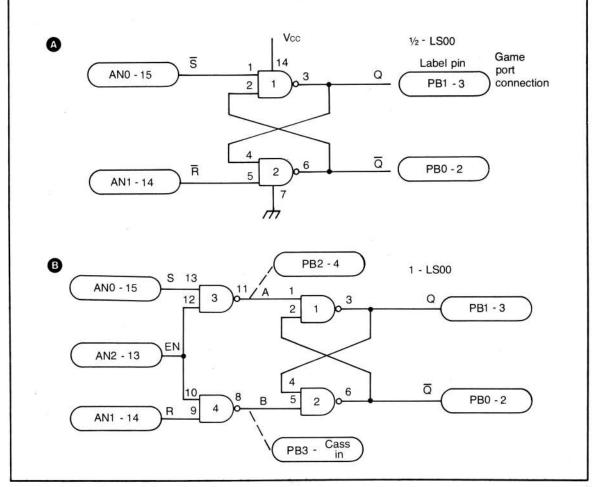

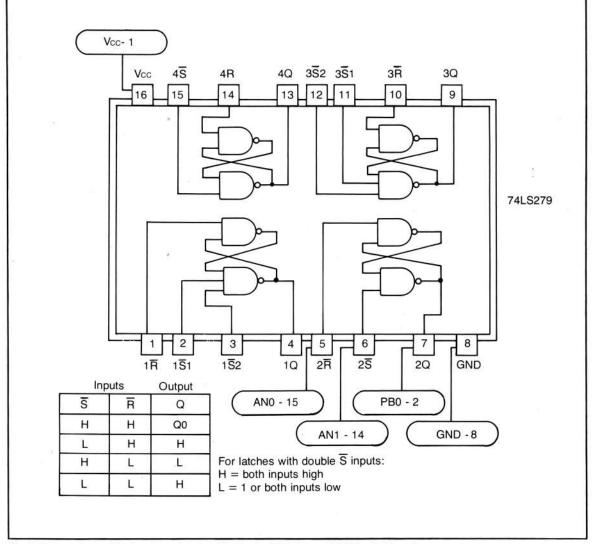

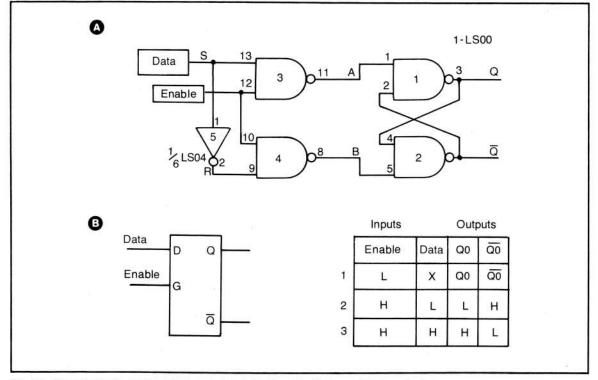

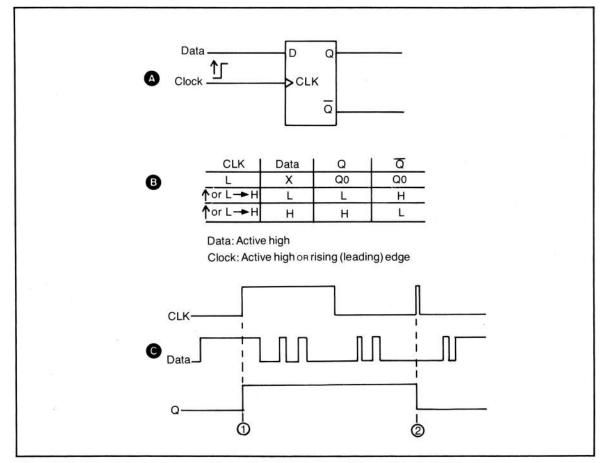

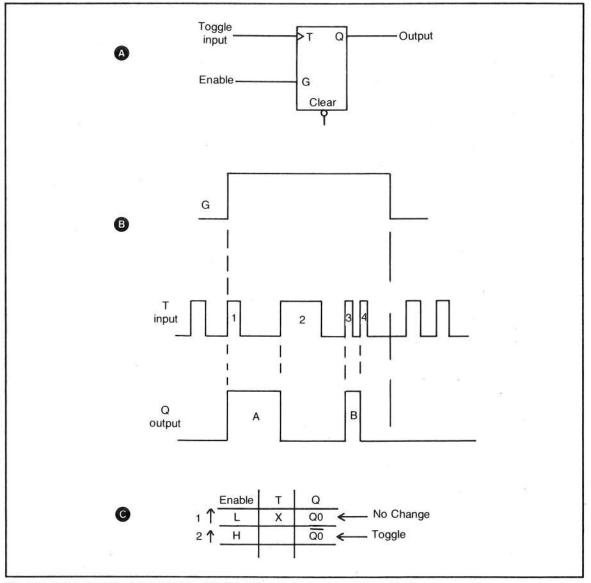

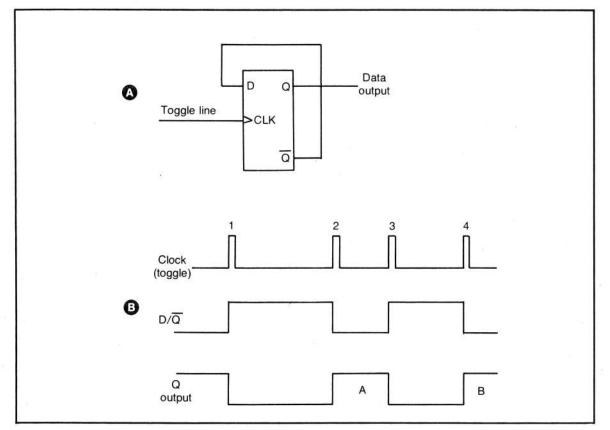

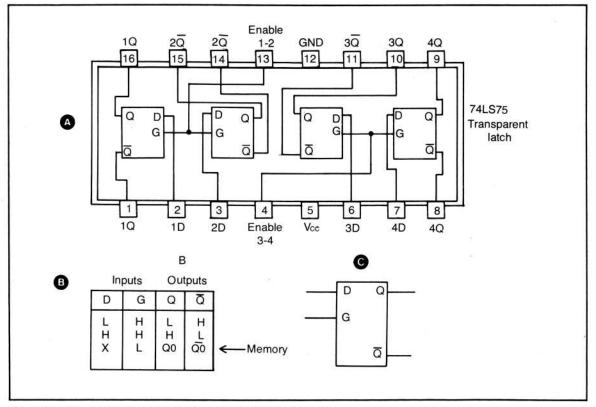

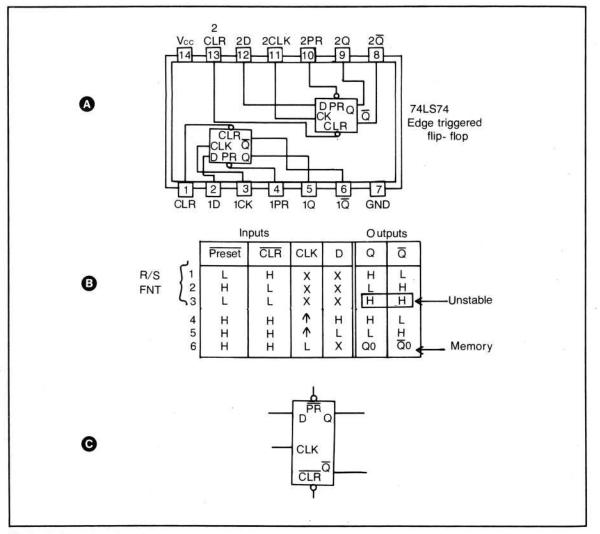

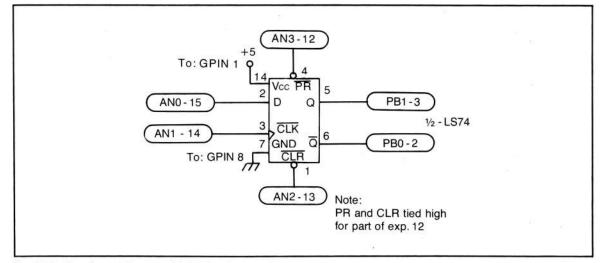

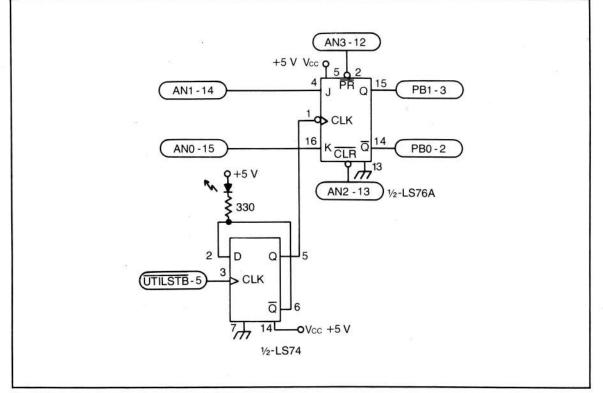

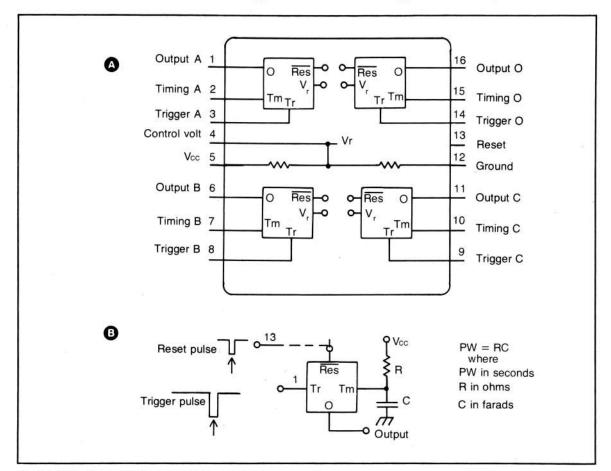

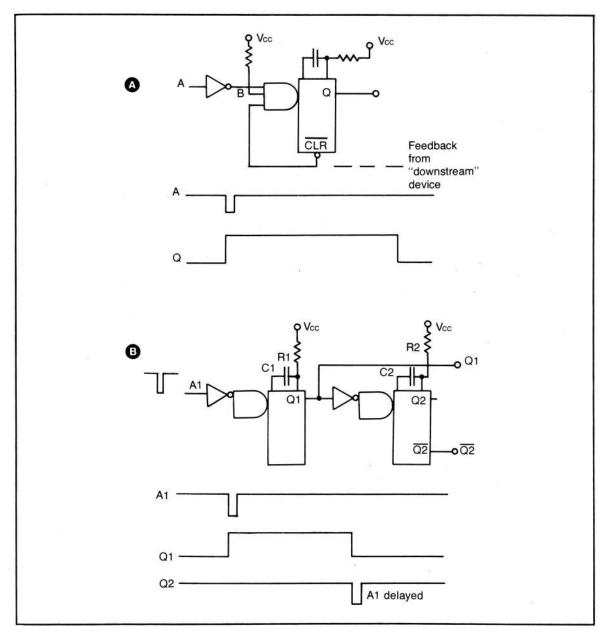

# 8 SSI Sequential Devices

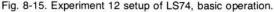

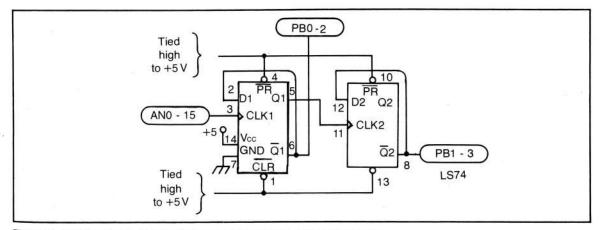

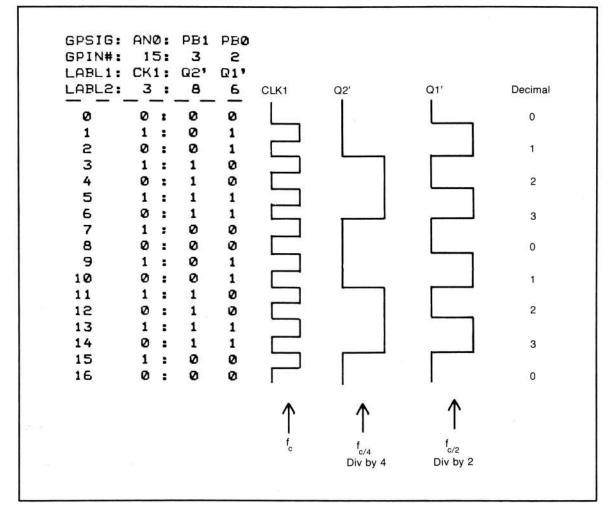

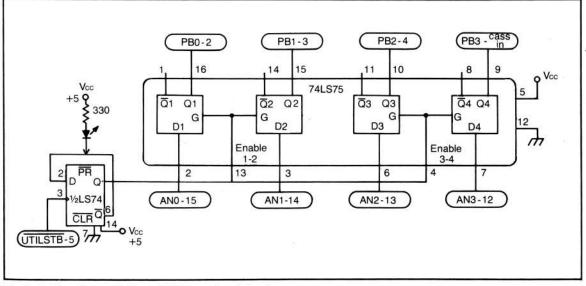

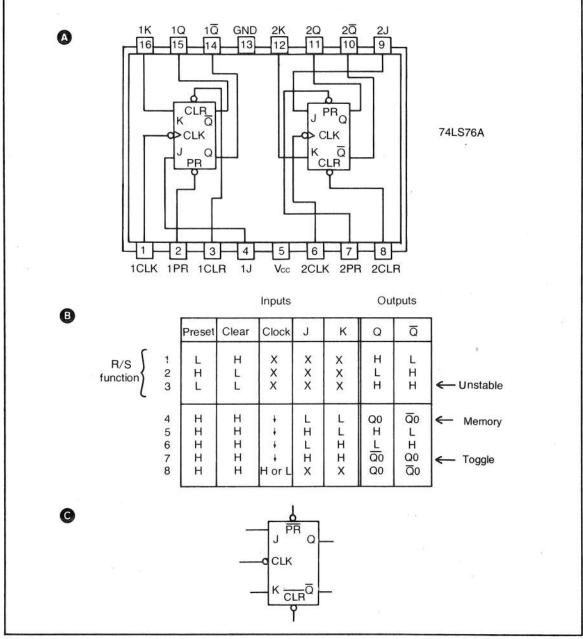

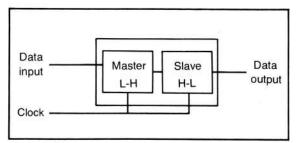

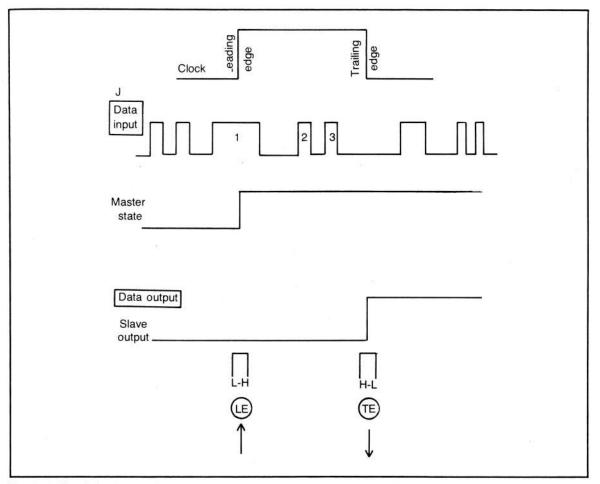

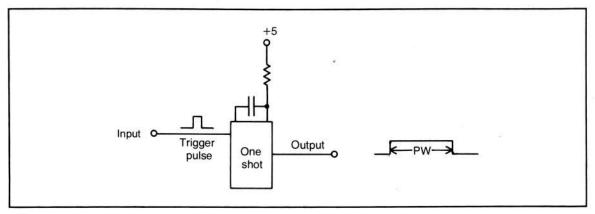

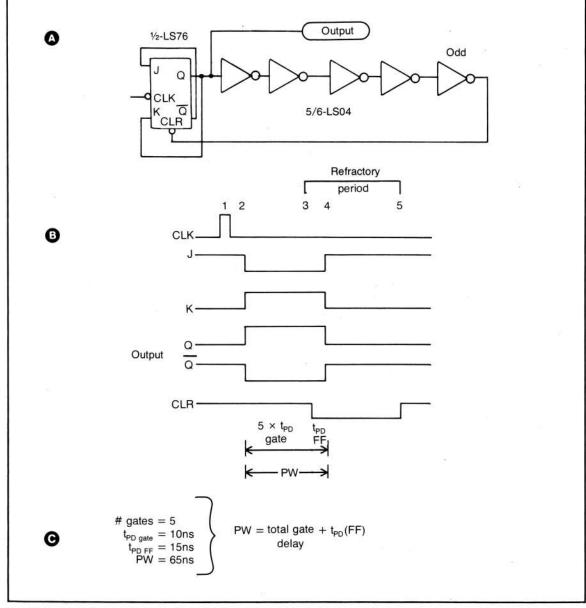

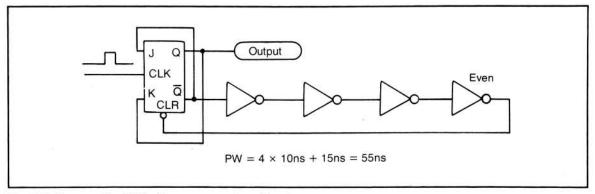

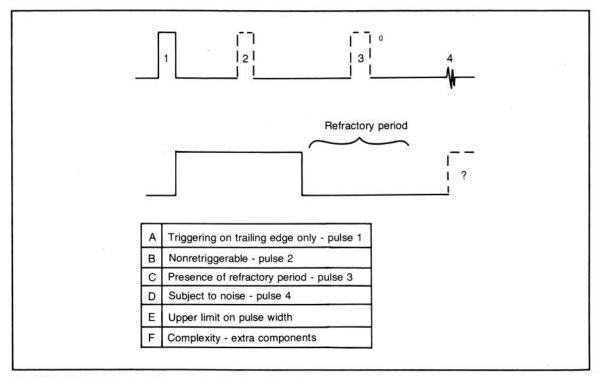

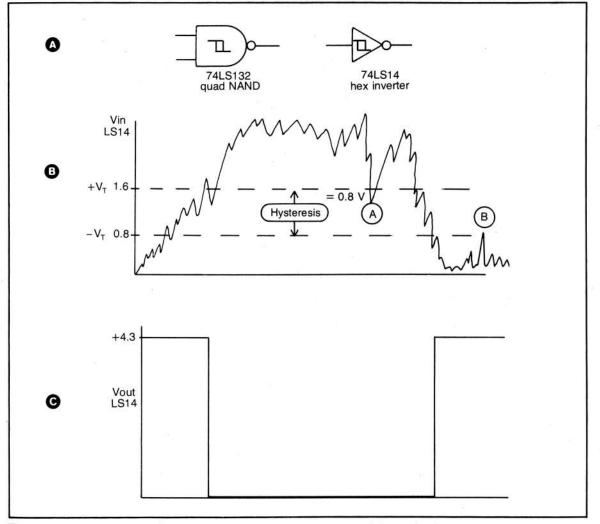

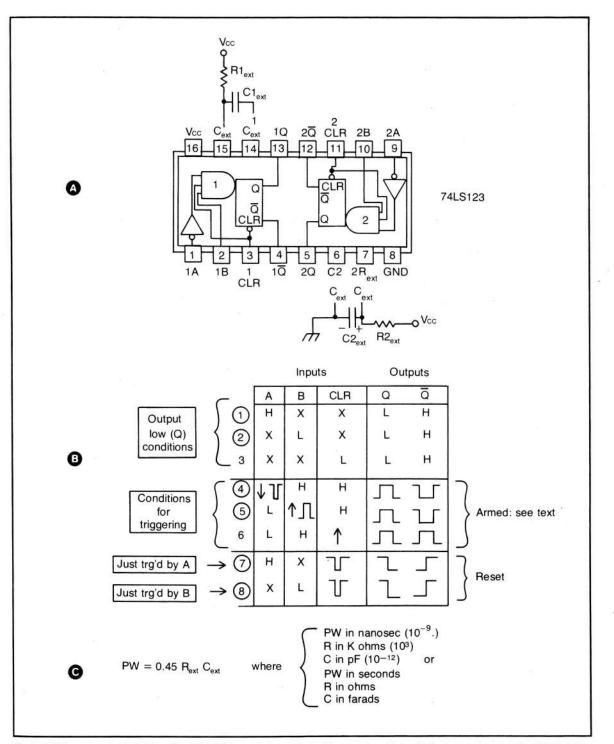

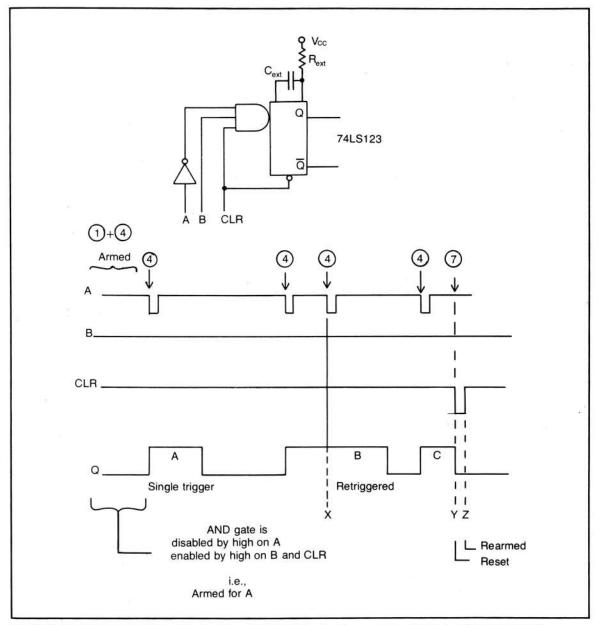

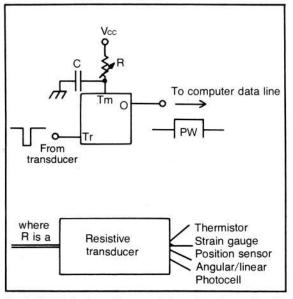

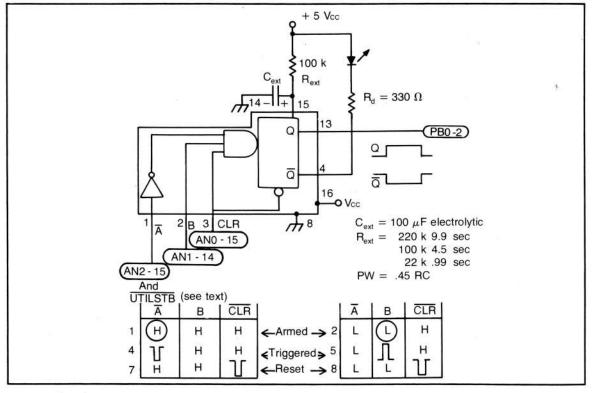

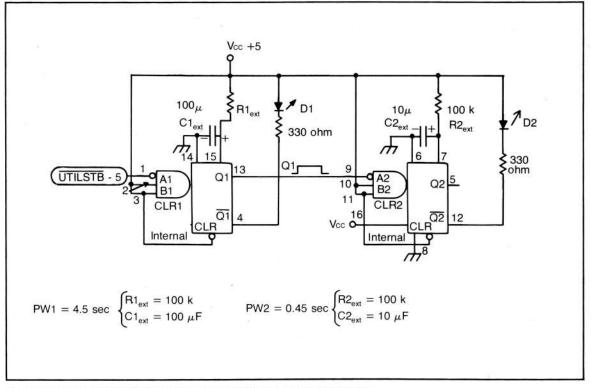

Types of Sequential Devices—R/S Flip-Flops—Clocked Logic Concepts—Experiment 11, R/S Latches—D and T Flip-Flops—Experiment 12, The LS74 Flip-Flop—Experiment 13, the LS75 Quad D-Latch—The J-K Flip-Flop—Experiment 14, The J-K Flip-Flop—Monostable Devices or One Shots—Experiment 15, The One Shot

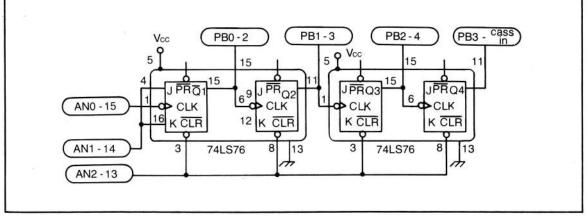

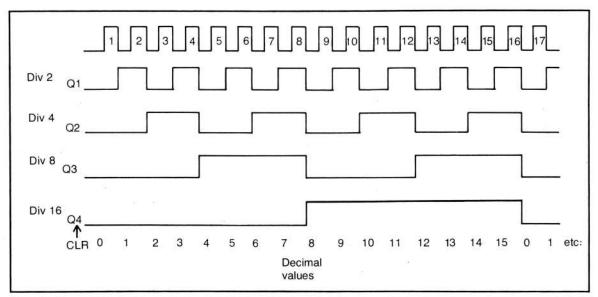

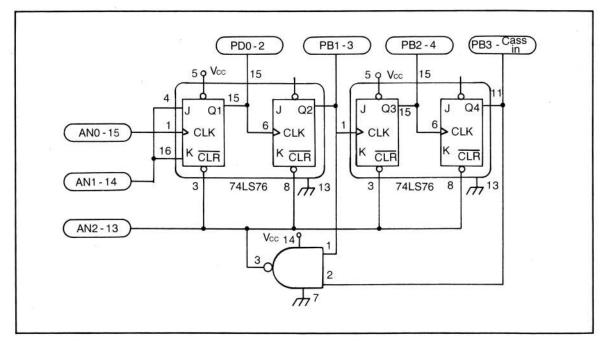

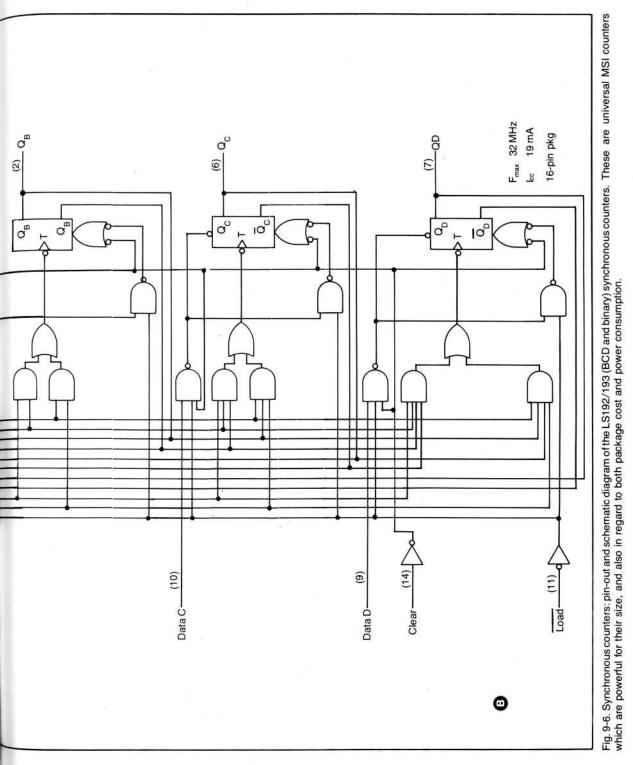

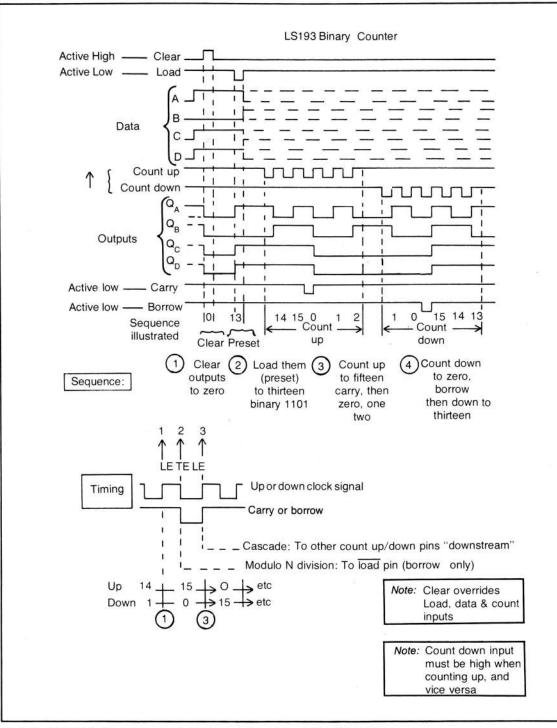

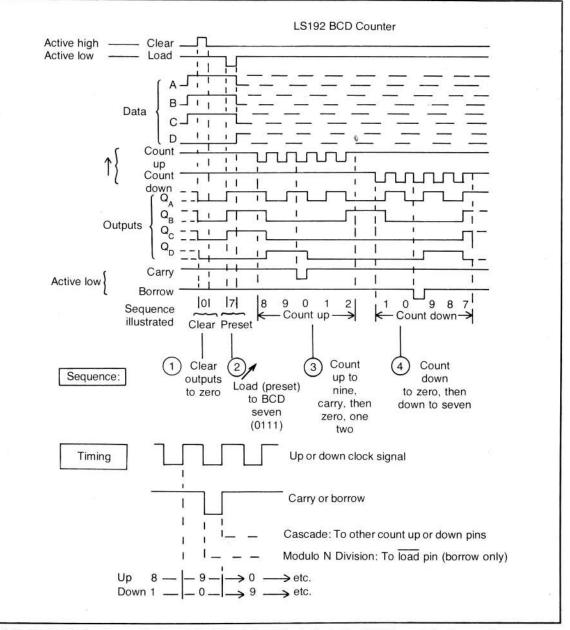

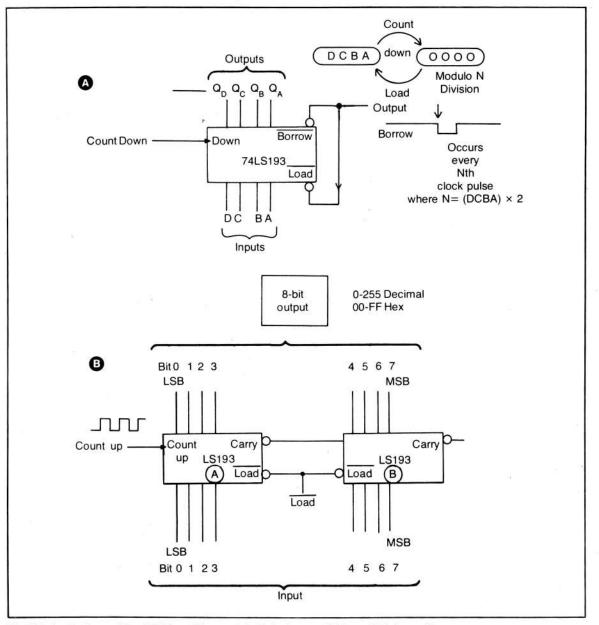

# 9 MSI Sequential Devices

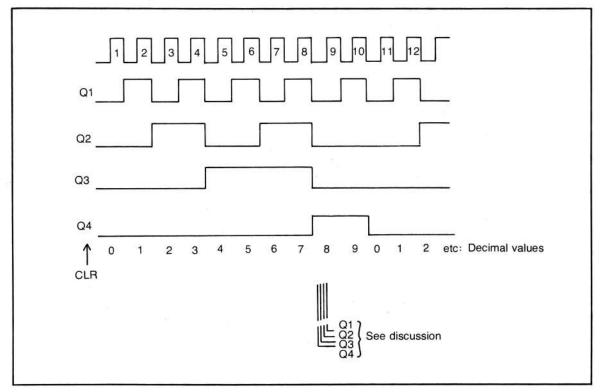

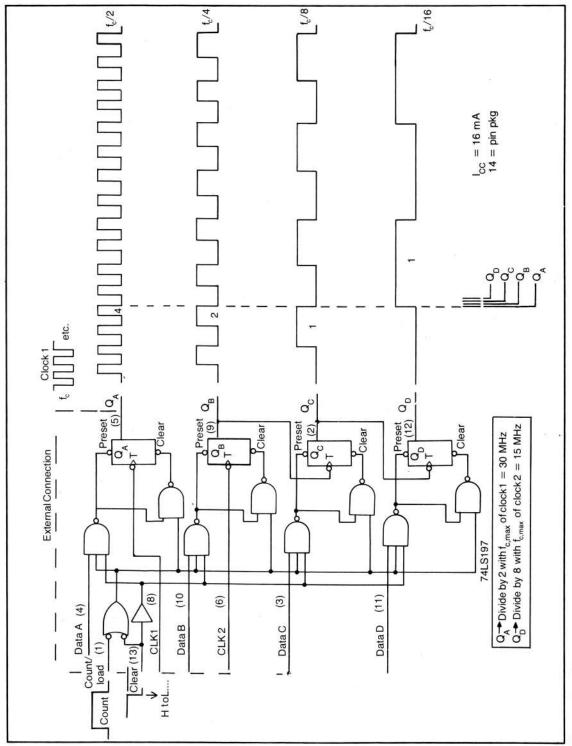

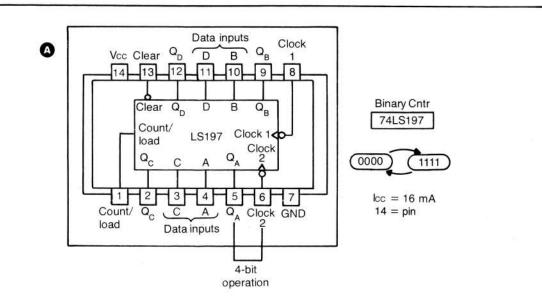

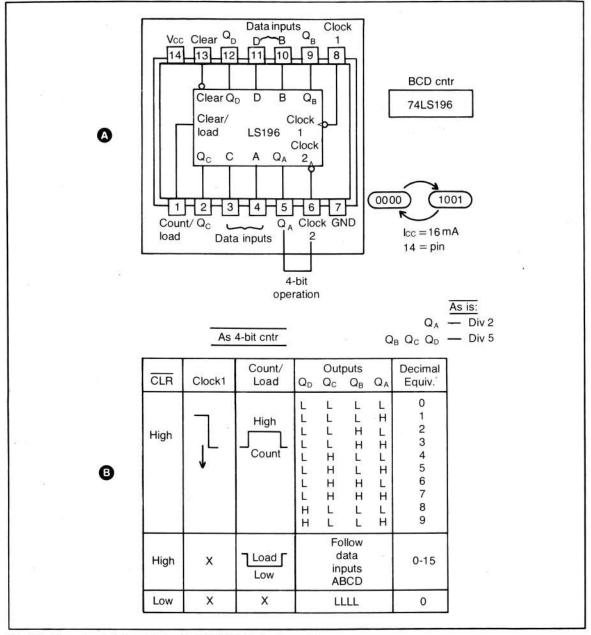

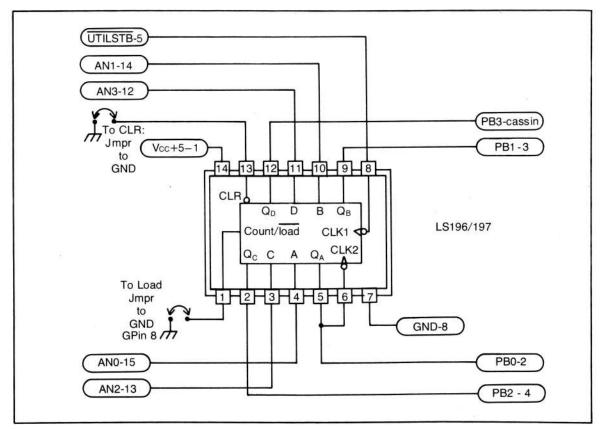

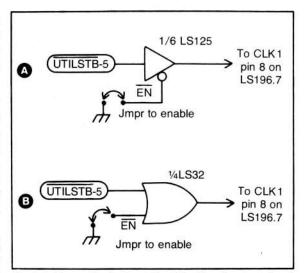

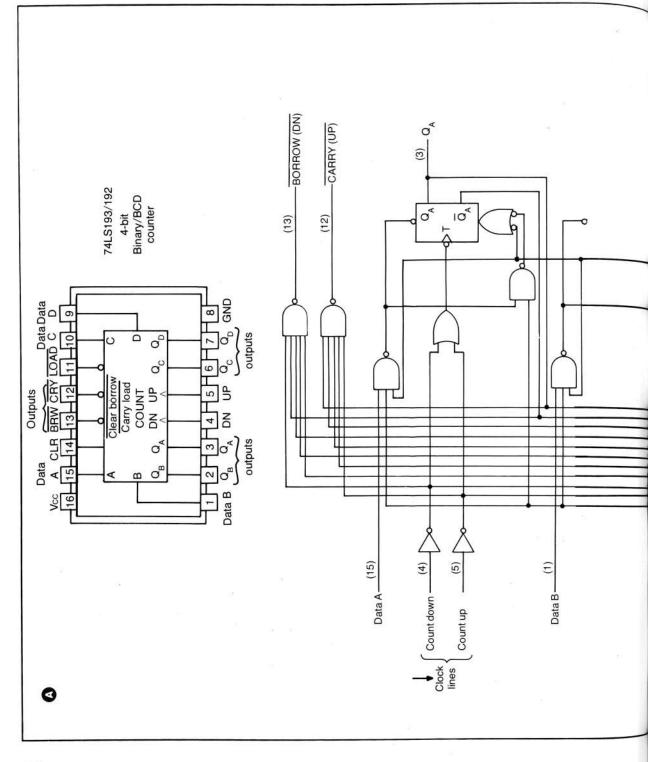

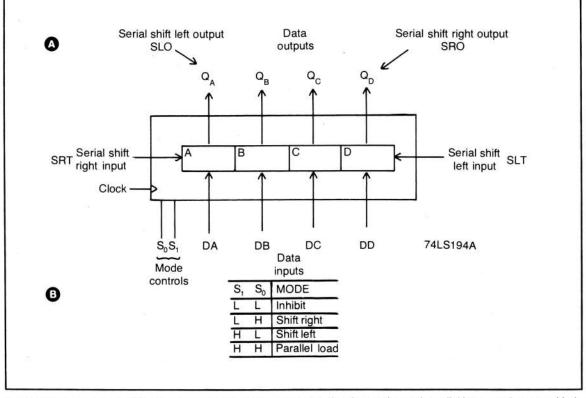

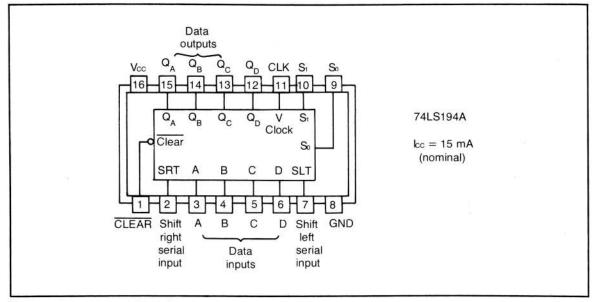

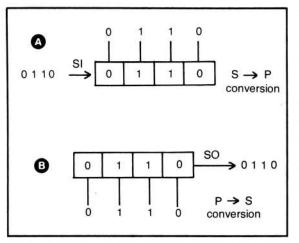

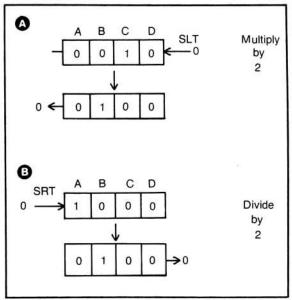

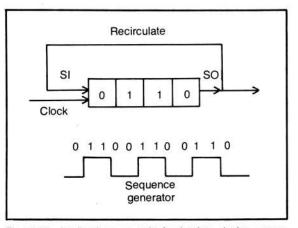

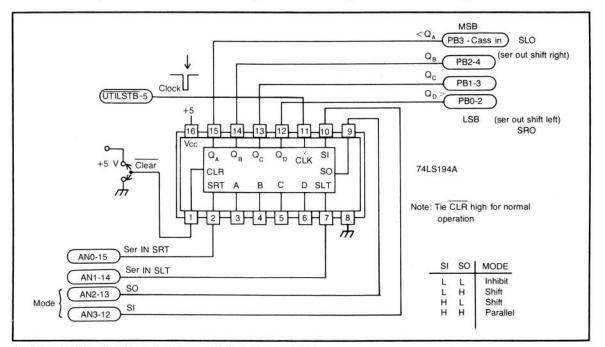

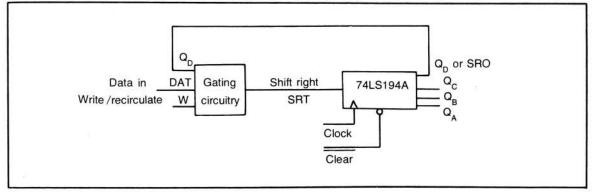

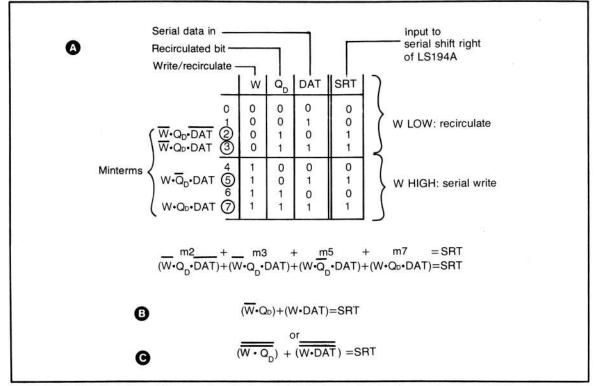

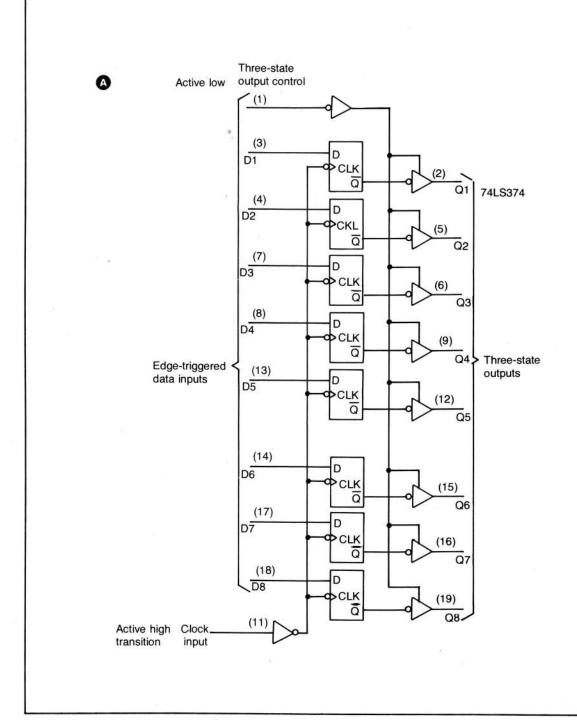

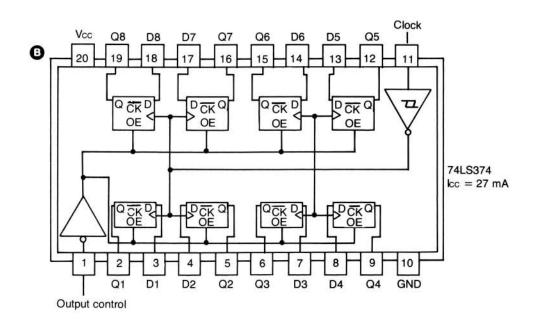

Medium Scale Integration—Ripple Counters—Experiment 16, MSI Ripple Counter—Synchronous Counters—Experiment 17, The Synchronous Up/Down Counter—Shift Registers—Experiment 18, The Shift Register—MSI Latches

# 10 Combinational MSI Devices

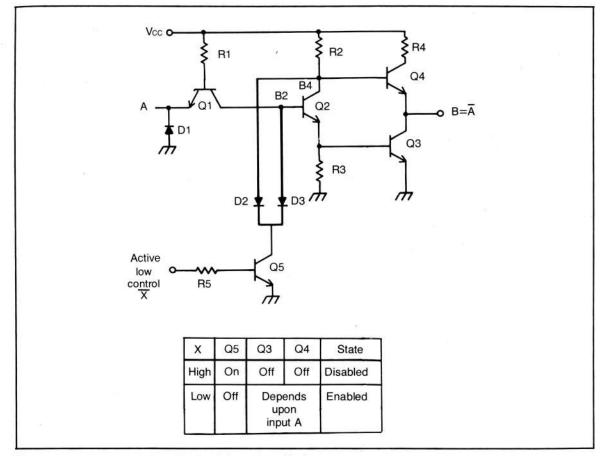

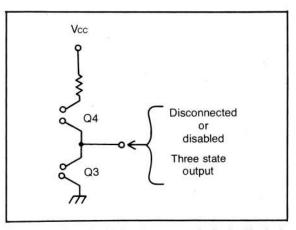

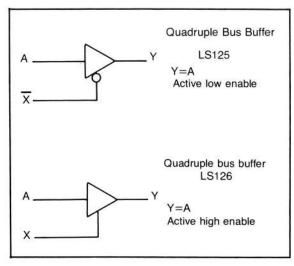

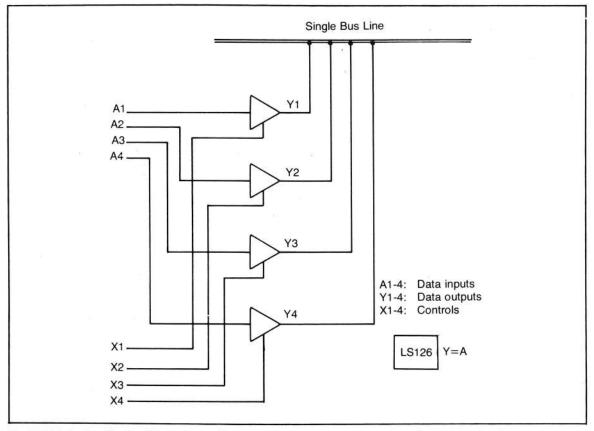

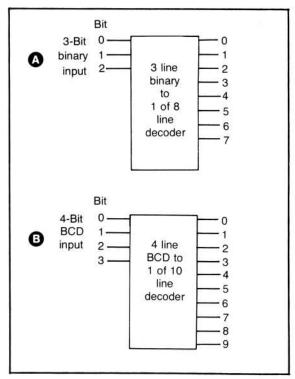

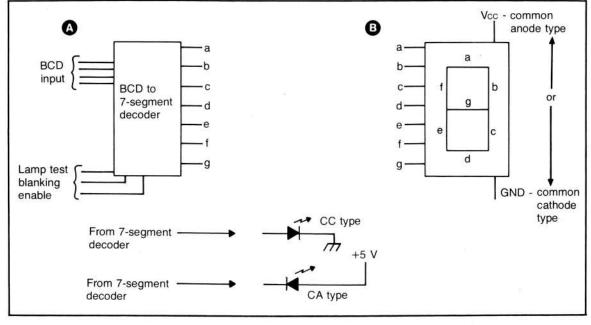

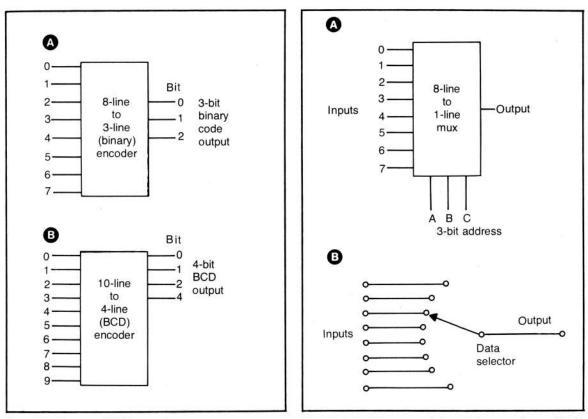

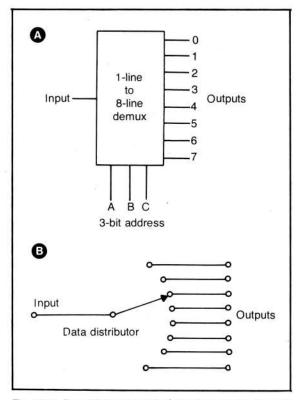

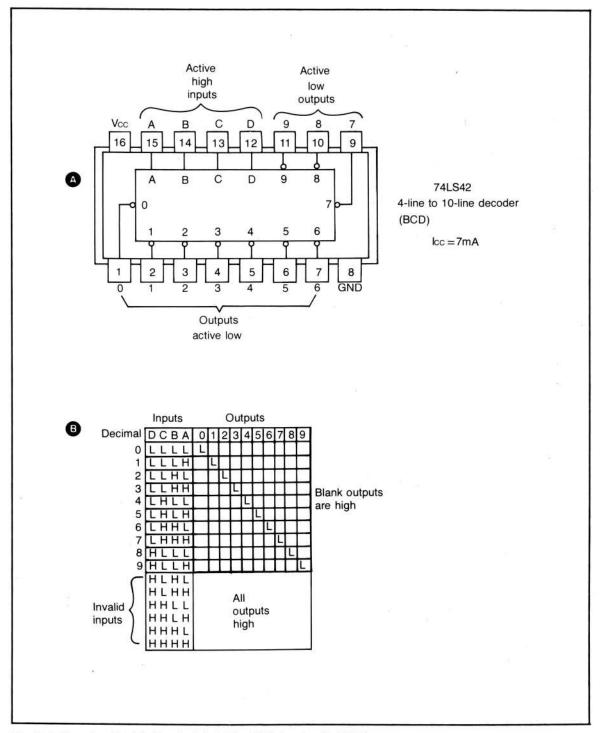

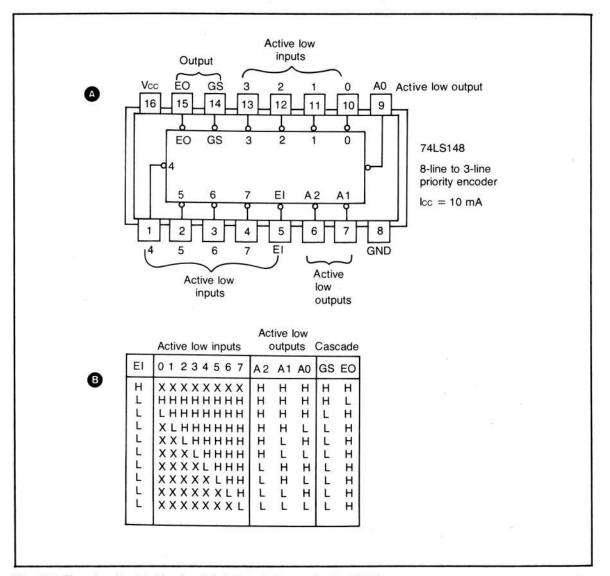

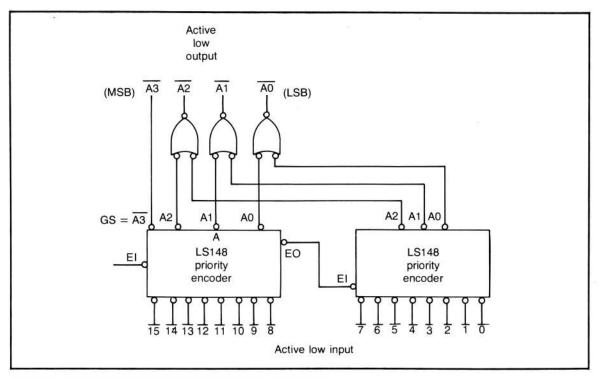

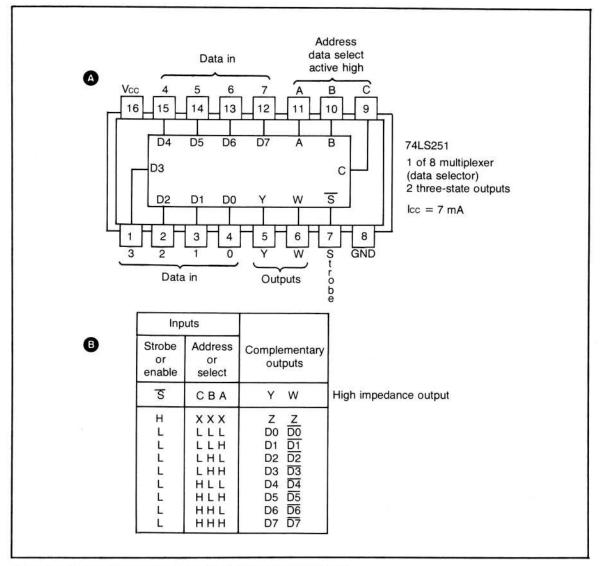

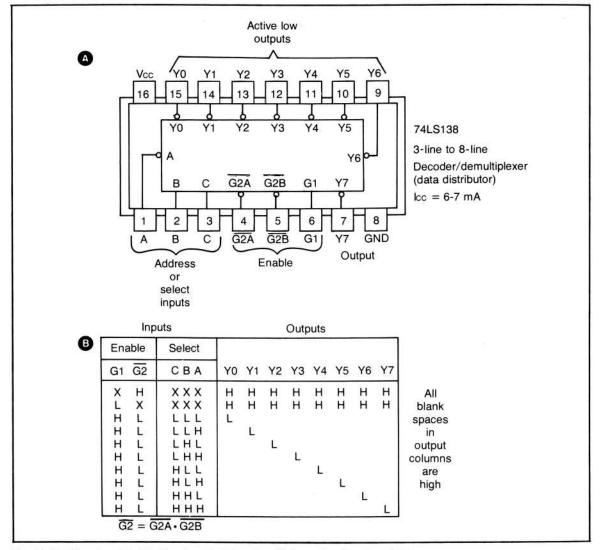

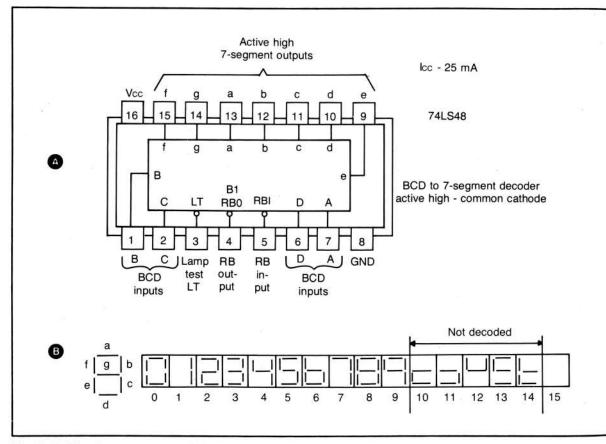

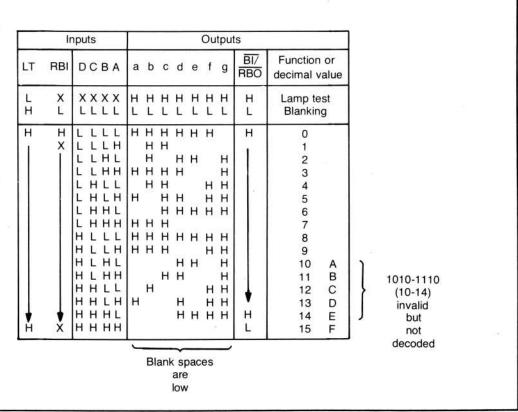

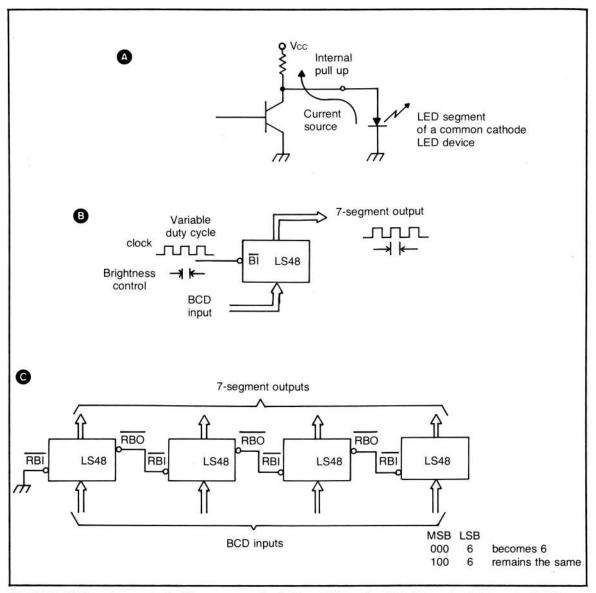

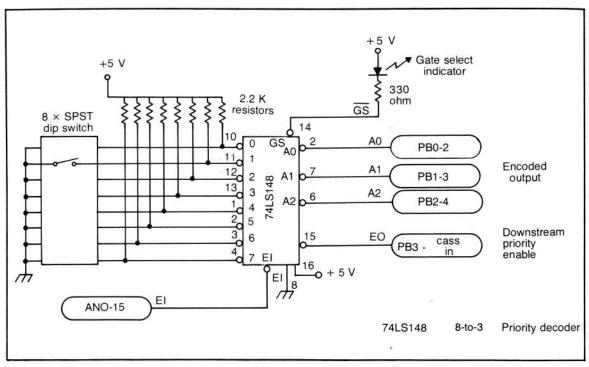

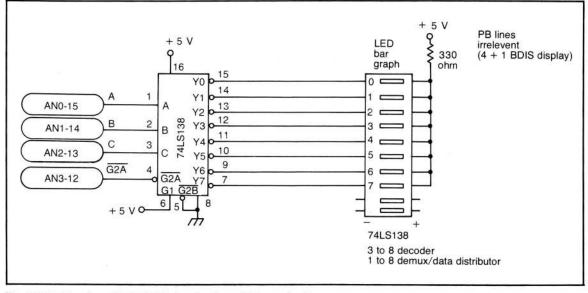

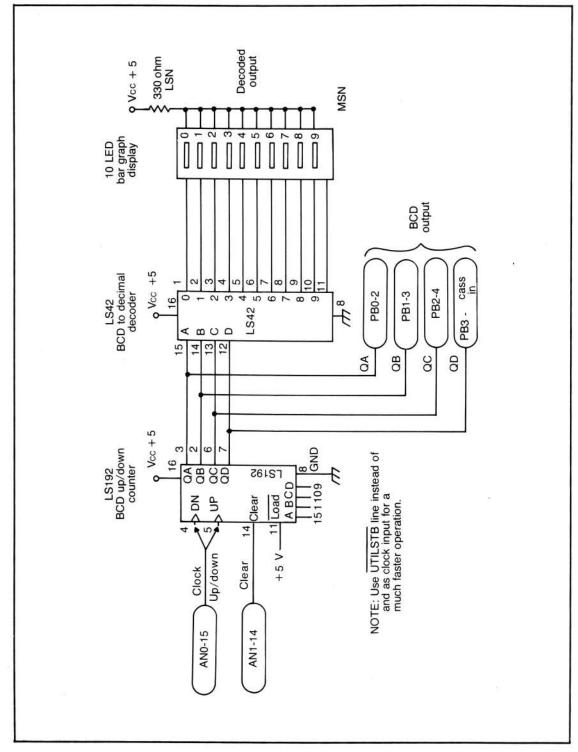

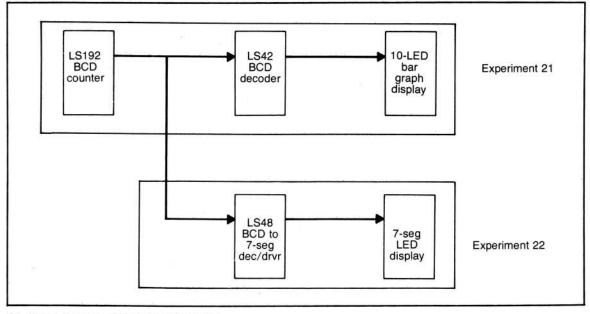

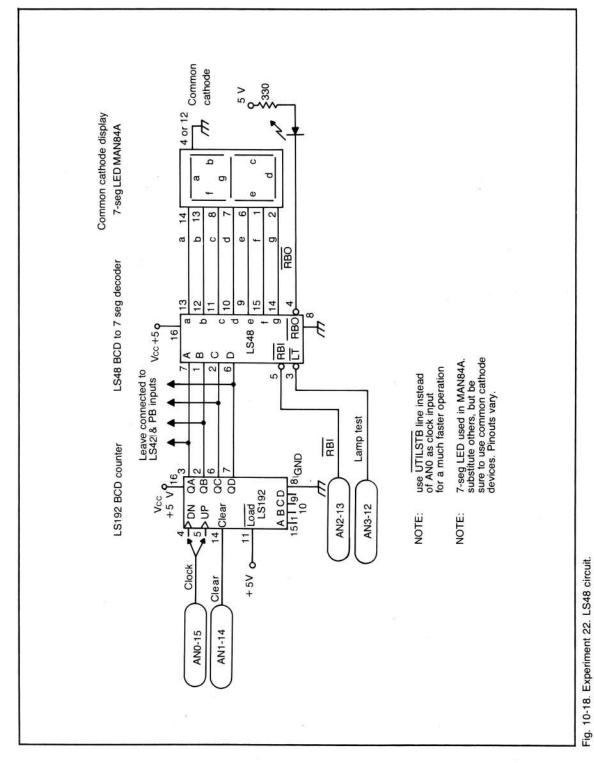

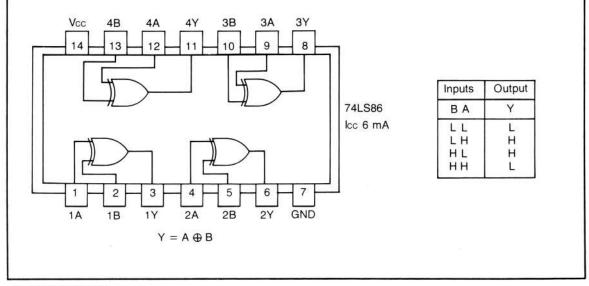

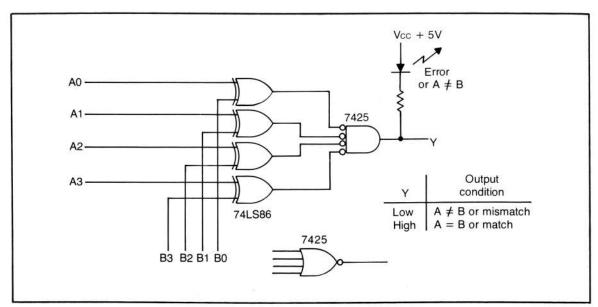

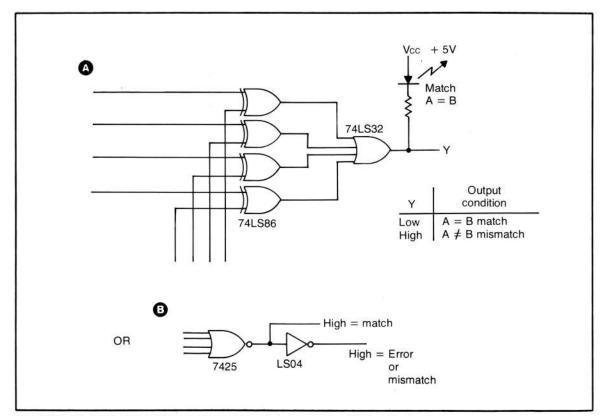

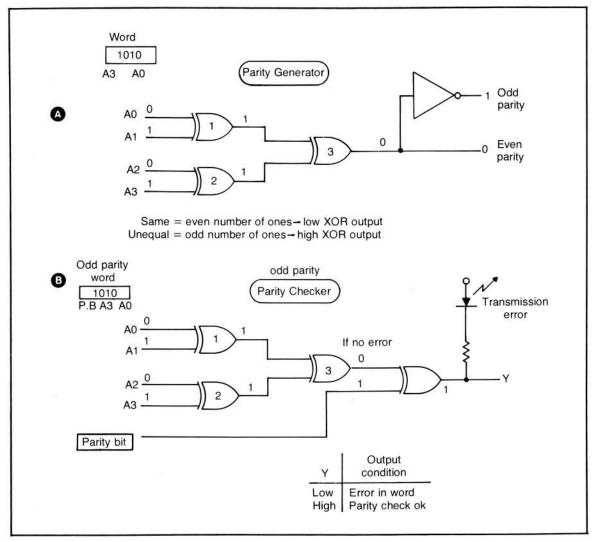

Code Conversion and Data Routing—Experiments for MSI Combinational Functions—Experiment 19, Priority Encoder—Experiment 20, Binary Decoder/Demultiplexer—Experiment 21, BCD Decoder—Experiment 22, Seven-Segment Decoder/Driver—Three State Devices—Exclusive-OR Functions

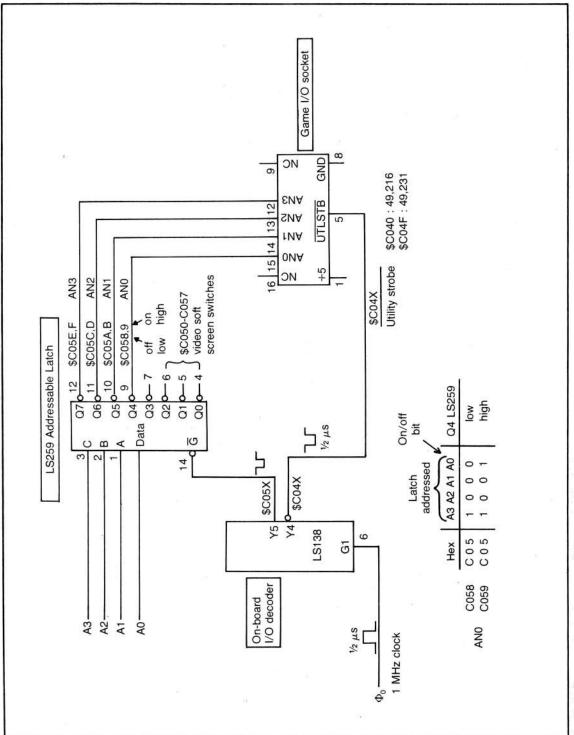

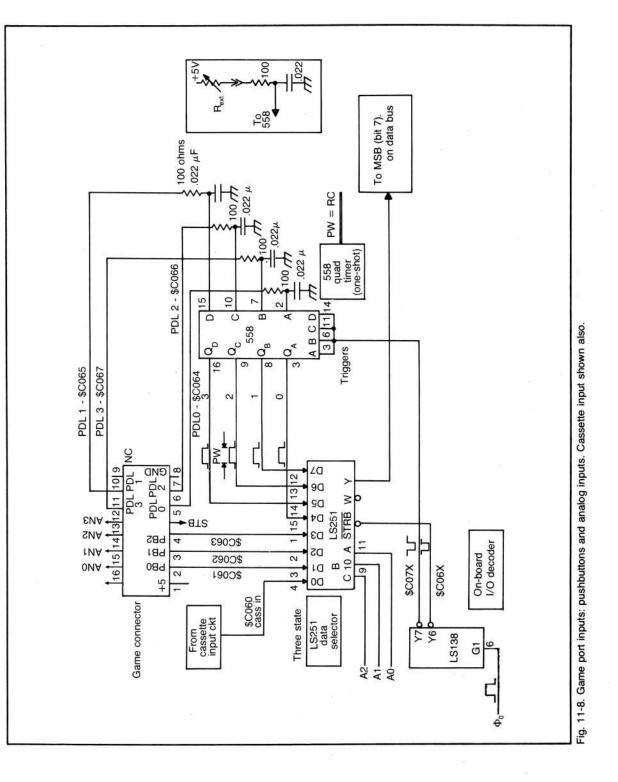

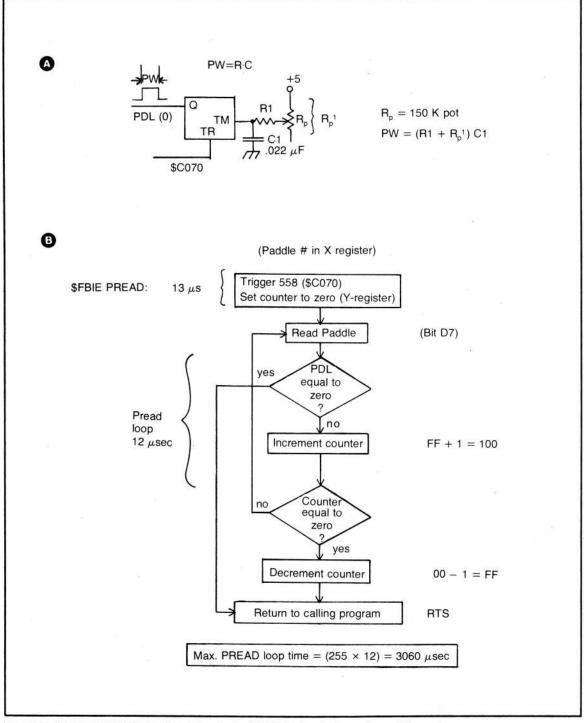

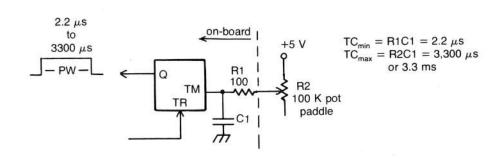

# 11 An Introduction to Interfacing

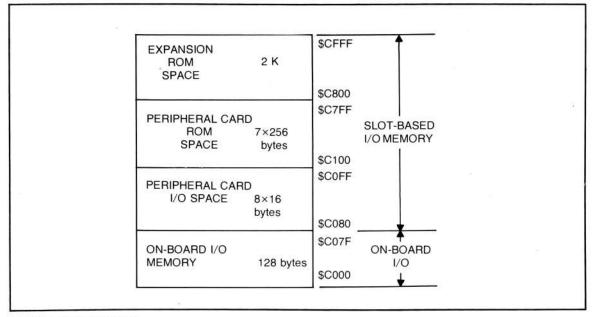

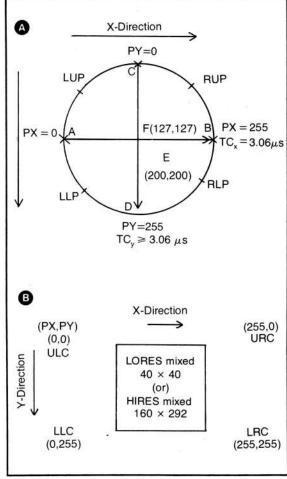

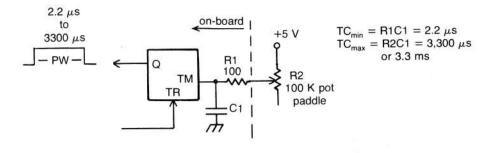

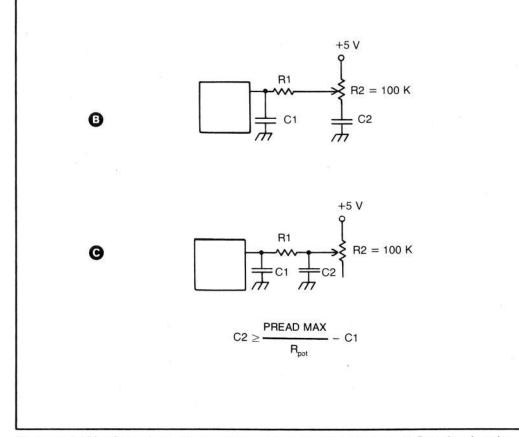

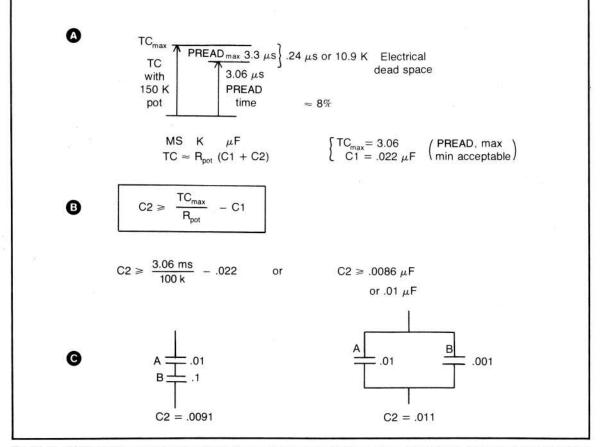

The I/O Triad—The System and I/O Memory Maps—I/O Address Decoding—On-Board I/O Circuitry— Simple Applications Circuits—LORES/HIRES Joystick Project—Closing Comments

# Index

161

189

233

269

299

338

# Introduction

This book began with a simple idea: to teach the basics of digital electronics in a hands-on manner using the desktop microcomputer as the primary learning tool.

This primer is not a cookbook of circuits. Instead, it provides an approach that will allow you to acquire a basic but thorough knowledge of digital devices and techniques and the ability to apply these skills to more complex and interesting projects.

Because it is assumed that you have little or no knowledge of electronics (digital or otherwise), one of the major goals of this book is to provide you with a knowledge of essential electronics. Too many books assume this knowledge and jump into digital electronics right away. The other broader and more intensive emphasis is on the digital IC chips themselves: what they do, how to specify them, and how to use them to perform simple tasks. Familiarity with basic electronics and with a variety of IC chips from the major functional categories will together give you a firm foundation for future progress. Some additional, specific aims include helping you gain competence in reading and using the technical data and applications literature, in designing smallscale circuits for specific functions, in interpreting digital schematics (such as the Apple main board diagram), and even interfacing your computer for simple I/O (input/output) applications.

Once you've been grounded in these fundamentals everything else—including computer hardware applications—are nothing more than extensions to this knowledge. The intention is to give you a firm base for advancement.

# TOOLS

Learning demands doing. Digital electronics is as much a set of skills as it is a body of knowledge. Your competence in this field depends as much on your working with a variety of digital devices as it does on knowing their function. Handling, testing, and building a circuit using a device gives you a range of stimuli not obtainable from passive study. The more ways you are exposed to a subject, through the fingers as well as through the brain, the better you will understand it. Like many micro owners who want to learn about the digital hardware, you may be hesitant and uncertain about how to satisfy your curiosity. The would-be experimenter faces the prospect of first acquiring a logic trainer, boxes of parts, and barrels of equipment before embarking on his projects or studies. This costly and time-consuming process is unnecessary. A powerful educational tool is already at your disposal—the Apple computer itself!

The microcomputer has been touted for a long time as a "solution in search of a problem" and as a "universal tool." So it seemed logical that this powerful all-purpose machine could be adapted to teaching the fundamentals of digital hardware.

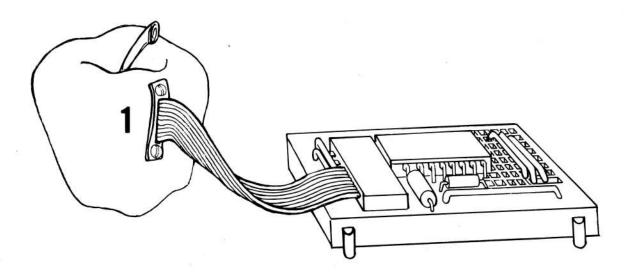

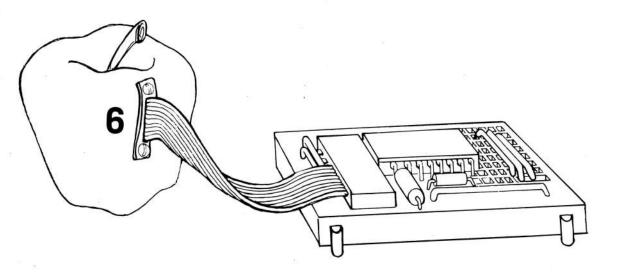

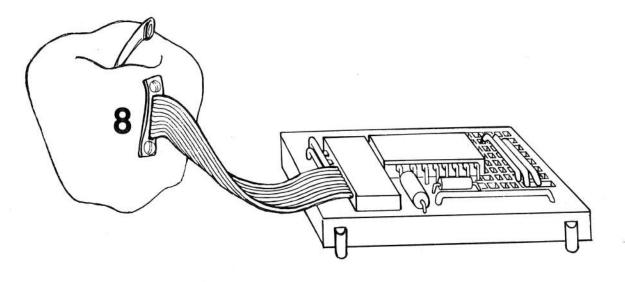

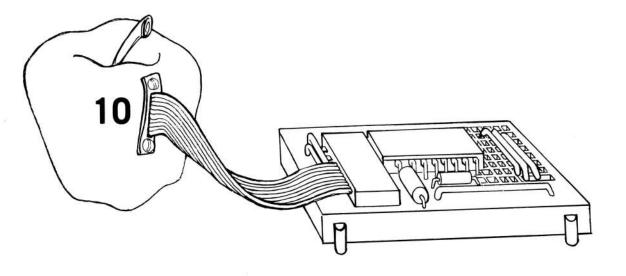

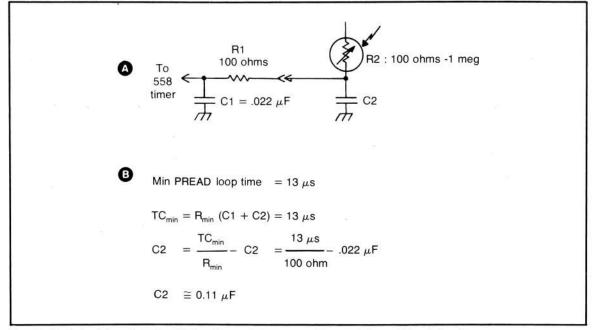

By exploiting the economy and simplicity of the Apple game port, you can turn this microcomputer into a digital desktop laboratory with very little effort and minimal expense. You will control game port signals via an Applesoft utility program—the Breadboard-In Software—that converts the monitor screen into a dynamic, reconfigurable display. What happens in the circuit is reflected on the screen, from moment to moment, even as you change signals. This arrangement eliminates most of the inconvenient preliminaries, yet retains all the advantages of the hands-on experimental approach.

### METHOD

Because a broad range of material is covered in the Apple Digital Hardware Primer, particular attention is given to the method of presentation. The value of maintaining a consistent level of difficulty, while at the same time building on preceding material, is obvious.

I don't cover every imaginable topic. Rather, the coverage is selectively deep in what you have to know. The emphasis is on basic skills and key concepts.

In this book you will do more than just demonstrate the functions of many digital IC chips. You learn how to describe their function using formal methods and to use them in design by means of Boolean algebra. Also, you learn not only what they do, but how they work—the electronics inside the IC packages. This allows you to use them safely and effectively in actual physical circuits. Further, the principles and practices introduced are related to computer operation—bus organization, interfacing principles, memory decoding, etc.

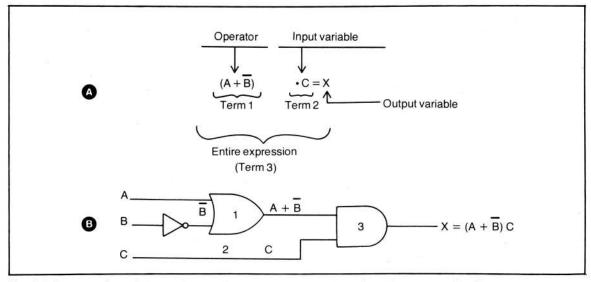

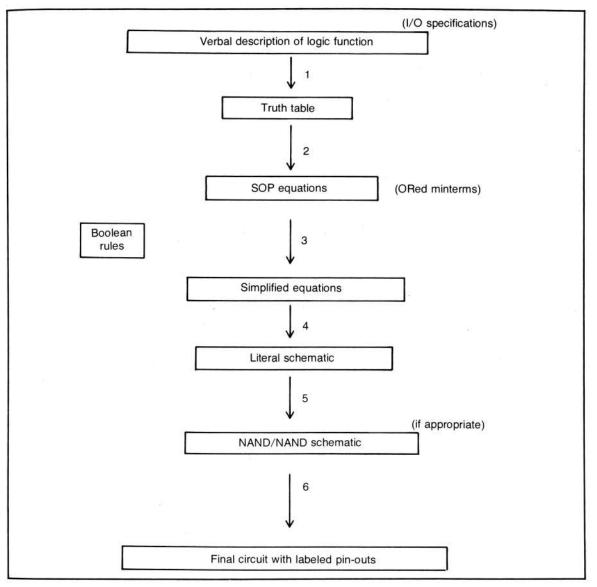

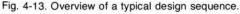

After a general survey in Chapter 1, you are shown how to set up your desktop digital laboratory in Chapter 2. Other "tools" are developed as part of the overall organization. You will first study the digital IC as a "black box," as a functional unit rather than as an electronic circuit. Function is emphasized. You learn about basic "building block" chips (combinational SSI devices) in Chapter 3, and then see how formal Boolean methods can be applied to digital design using this important group of ICs (Chapter 4).

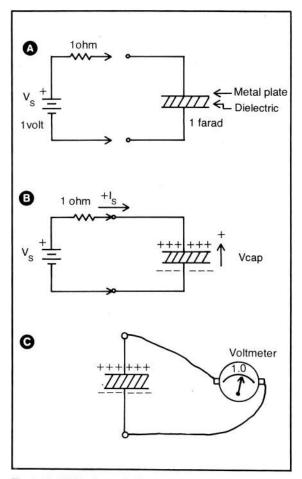

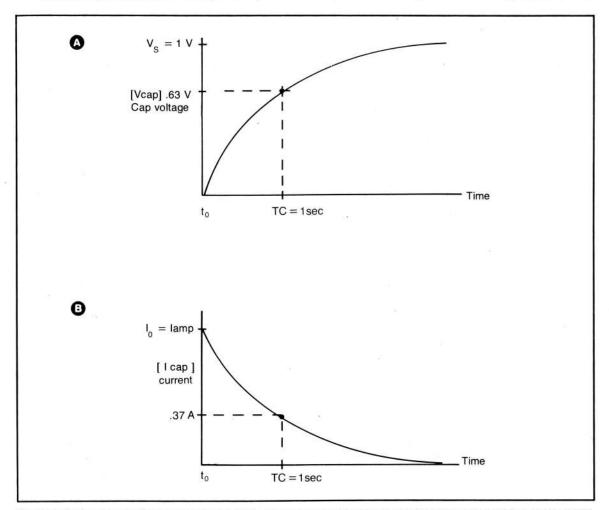

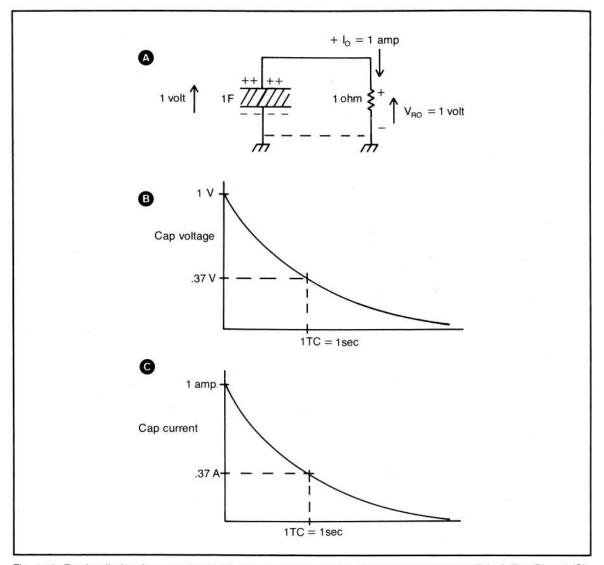

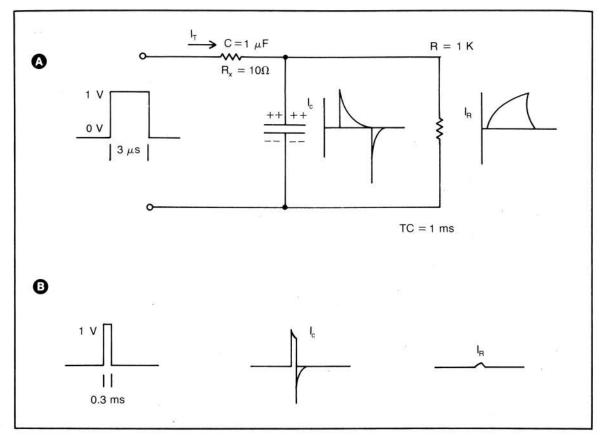

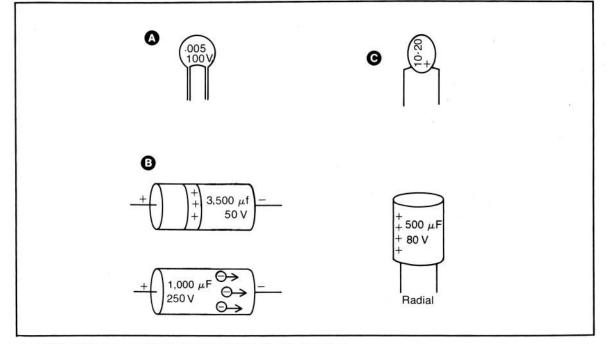

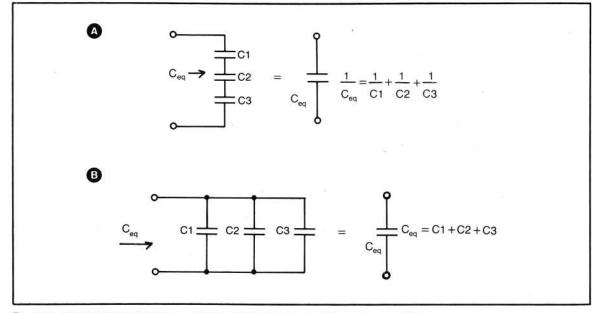

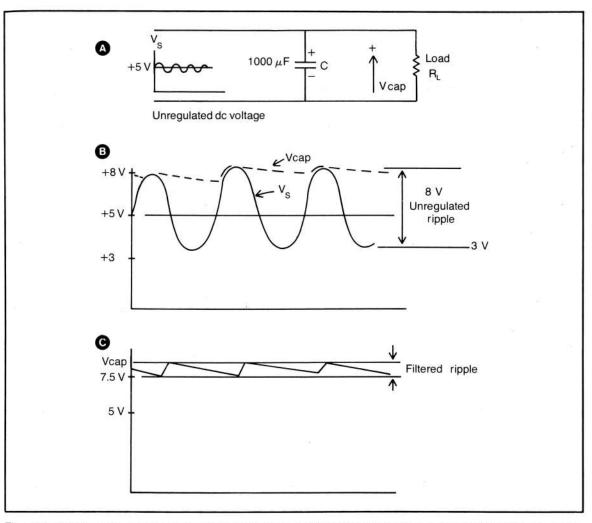

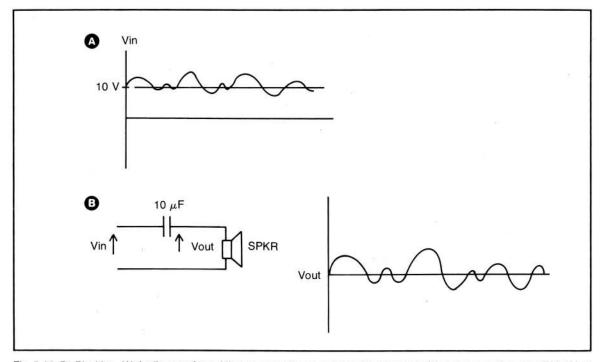

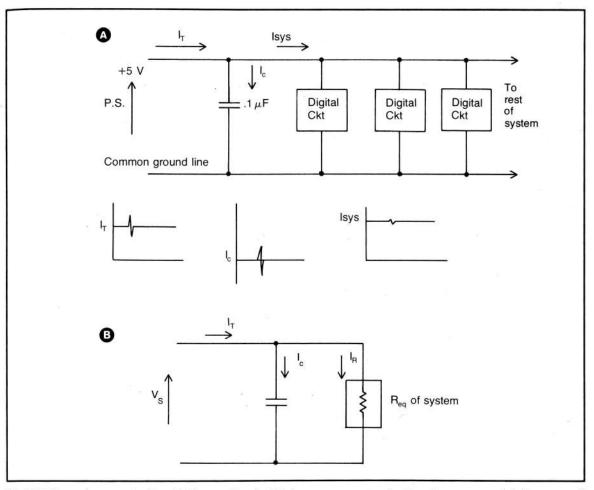

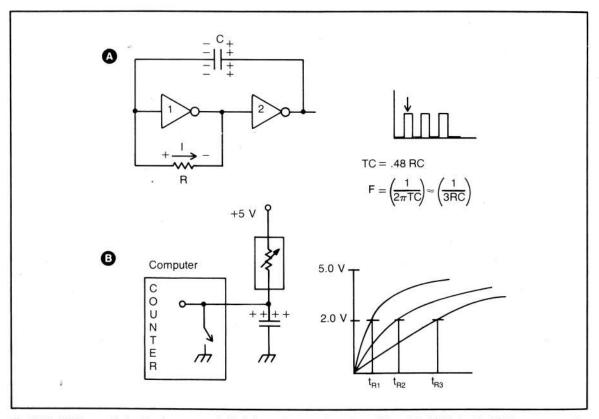

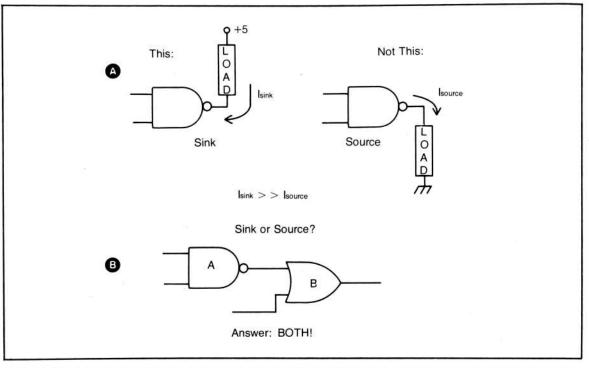

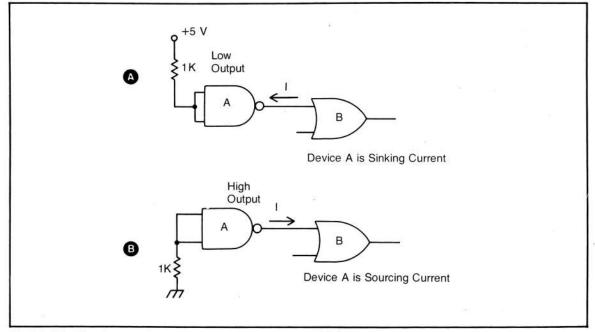

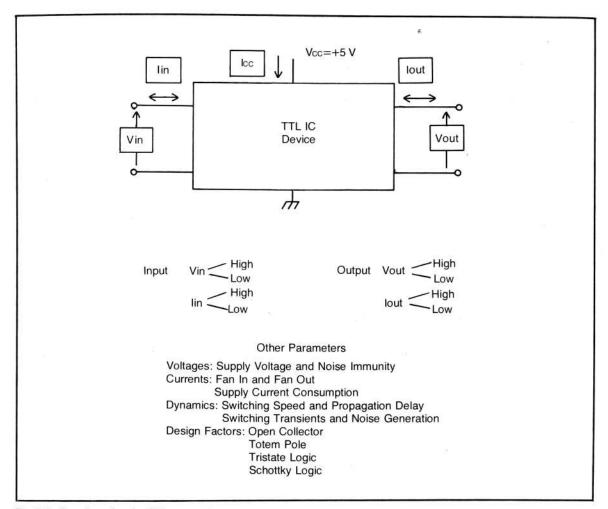

Chapters 5, 6, and 7 comprise the "essential electronics" section. You learn about discrete electronic components and their laws of operation (capacitors, resistors, diodes, and transistors). Then you apply this knowledge to the operation of a typical digital IC. At the end of this section, you will be quite comfortable with concepts like fan-out, despiking, current sinking logic, capacitative loading, and totem-poles. Data manuals and the technical specifications they contain will no longer be a mystery. You'll use them with facility and confidence.

You then can tackle the area of sequential devices in Chapters 8 and 9. Both SSI and MSI levels of integration are detailed, with representative chips from each category. Then in Chapter 10, the important MSI combinational chips are covered.

In all of the above chapters, experimentation plays a critical role in the presentation. Sometimes problems are presented as part of the experiments, so that they are more than mere demonstrations.

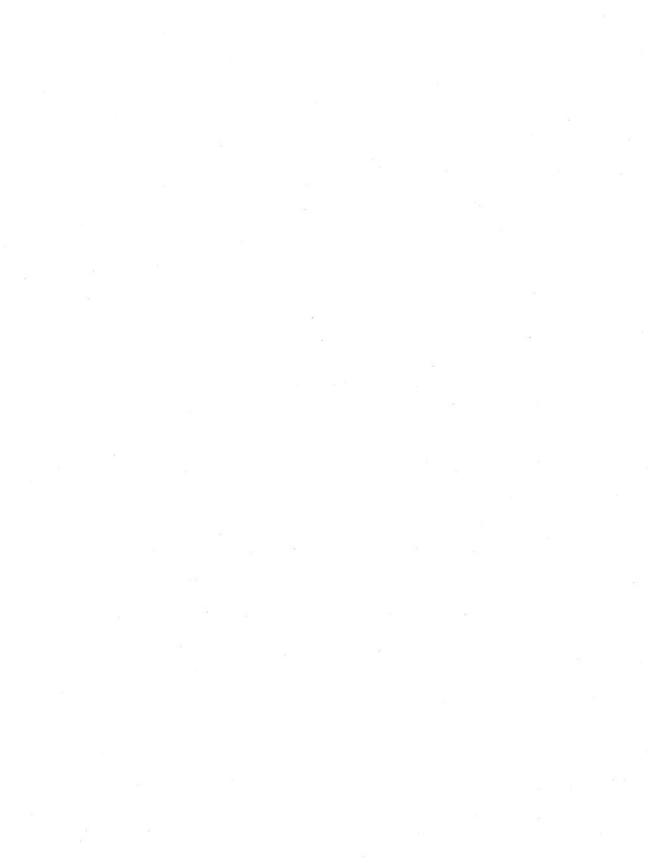

Chapter 11 concludes the book with coverage of some important topics in computer hardware applications under the general heading of interfacing. This chapter rests on the foundations laid down in the previous material. General principles are supported by a chip-by-chip description of key I/O circuitry on the Apple main board. Memory mapping and address decoding are dealt with in detail, using the Apple as an example. A few projects using resistive transducers for simple A D conversion close the book.

# **Fundamentals of Digital Electronics**

The digital integrated circuit is more than just a popular symbol for modern electronic technology. It is the basis for learning about that technology. In fact, the rationale for this book is that in-depth knowledge of representative digital integrated circuits—how they work and what they do—is the basis for your competence in digital electronics. In this chapter, you'll survey the role of the digital IC and get a preview of the material to be covered in later chapters.

# THE CHALLENGE OF DIGITAL ELECTRONICS

Digital integrated circuits are more than just a new group of electronic components. A phenomenal amount of theoretical knowledge and engineering savvy has gone into the creation of these electronic marvels, popularly known as IC chips. Microelectronics, the technology behind these devices, has created entirely new areas of activity and produced dramatic changes in existing ones.

Consumer electronics, including home entertainment and personal computing, global satellite communications, office and factory automation, medical diagnostics and new graphics design tools are just a few examples of these new applications. Certainly, the IC chip deserves to be the symbol of this electronics revolution. Its impact on daily life is obvious even to the proverbial man on the street.

For you, the microcomputer owner, digital integrated circuits hold more than a mere casual interest. Your machine would not exist without them. More than that, you may have sensed that a knowledge of digital electronics opens up new possibilities—as a hobby, as an enhancement to your present job or as the basis for a new career. Whatever your specific motives, practical applications or sheer curiosity, it is assumed that you do have a strong interest in learning about digital hardware. It's also assumed that you possess little if any electronics knowledge, but that you are willing to put in the extra effort to learn the basics.

Digital electronics is a complex field. Even the more elementary material is challenging. There are so many terms, principles, and concepts that the

1

subject begins to take on the characteristics of a language. Thorough grounding in the basic concepts is especially necessary in digital electronics in order to avoid superficial cookbook knowledge. The whole concern of the first half of this book is to help you gain mastery of the fundamentals.

However, the major problem is not the difficulty of the subject matter, because your willingness to tackle it is taken for granted. Rather, the problem is that of paraphernalia. Let me explain.

Paraphernalia is a long story with a sometimes unhappy ending. It begins with the question, "What parts, tools, materials and equipment do I need to get started in learning digital electronics?" It continues with searches through the catalogs and the making of long lists. After you shop, then you order; then you wait, often for quite a while. When vour digital laboratory is assembled you can rightfully feel proud. And also a lot poorer. It is usually only when you start paying the bill that you realize that perhaps you overbought. You didn't really need that fancy dual trace oscilloscope, that function generator or that elaborate logic trainer-prototyping apparatus. In addition, it may take a while to gain proficiency in the use of this equipment before you can even begin experimenting.

Quite frankly, hardware enthusiasts do spend a lot of time and money on equipment and materials. There seems no other way to acquire the necessary hands-on knowledge of digital electronics other than to follow the scenario suggested above. And of course, quality equipment is worth it in the long run if you actually need it. But is it necessary to spend all that money as a beginner? Isn't there a better way?

#### THE MICROCOMPUTER SOLUTION

A powerful, all purpose tool already in your possession will help you to solve this hardware paraphernalia problem: the Apple microcomputer.

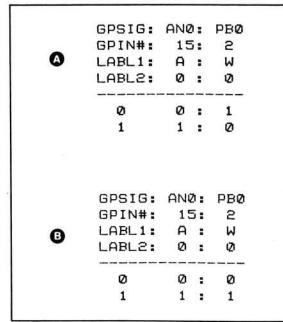

By exploiting the economy and simplicity of the Apple game port, you can turn this machine into a digital logic trainer/breadboard system with minimal effort and expense. You control the game port signals and monitor them via an Applesoft utility program—the Breadboard-In-Software (BDIS)—which turns the monitor screen into a dynamic, reconfigurable tabular display. All the signals sent to and received from the circuit under study are displayed in an easy to read form. This arrangement eliminates all of the costly preliminaries, yet provides all of the advantages of a conventional hands-on system.

This computer-based trainer offers other advantages. Meaningful labels can be assigned to the signals of the device or circuit under examination. Pin-outs may be specified for ease of circuit hookup. Display format may be altered for convenient viewing. A printout can be obtained for permanent records of your experiments if you desire. Also, BDIS continually monitors the outputs of the circuit under study and automatically updates the display.

All that is required is a jumper cable, solderless breadboard strip, and a half-hour or so to type in the Breadboard-In-Software (BDIS) utility program.

At this point it is tempting to present the BDIS utility, show how to make the simple game port connection, and then procede to some "flashing lights" demonstrations. We'll do these and many other things in the next few chapters. But first it is necessary that you have a clear idea of how you are going to study digital devices and circuits.

### LEARNING ABOUT DIGITAL DEVICES

You can look at any specific digital IC device from several different standpoints:

$\Box$  As a sealed black box which performs certain logical functions.

□ As a collection of discrete electronic components integrated on a tiny chip of silicon.

$\Box$  As the member of a particular family of devices which share the same electrical characteristics.

□ As representing a particular level of component density per unit area of silicon—a level or scale of integration.

Virtually all the things you should know about digital ICs fall into one or the other of these

categories. The first category mentioned, the black box view, stands apart from the rest. The next two categories both relate to what goes on inside the IC. The last category refers to the levels of functional complexity of ICs. Let's look at each item in turn.

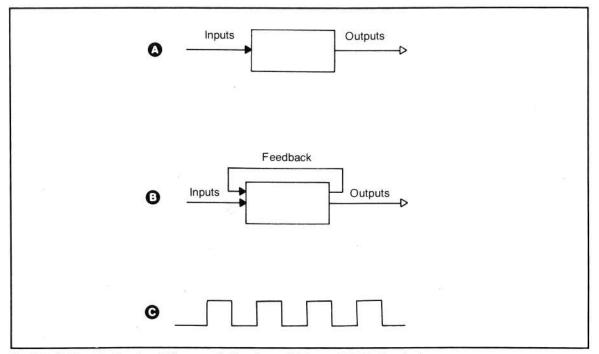

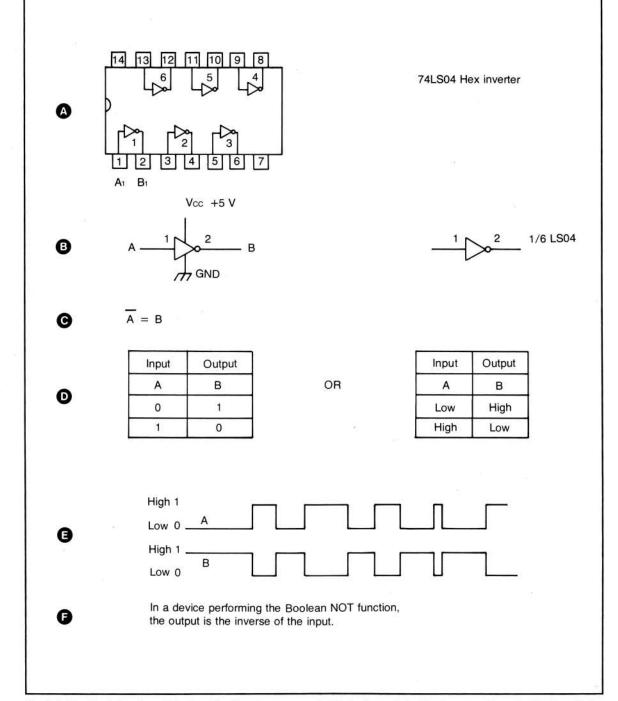

# DIGITAL DEVICES AS BLACK BOXES

The *black box* is a convenient engineering concept which is invoked whenever there is a need to simplify a complex process or system. If the object under study appears too complex you may, figuratively speaking, draw a line around it. By boxing in the system, you hide from view a lot of confusing internal detail. This technique makes it easier to understand how outputs are related to inputs. For the moment you don't care about what is going on inside the system, how the electrons do their chores, or how the system was manufactured (Fig. 1-1).

Fig. 1-1. With the black box approach, you don't care about the mechanism inside. Your concern is with function—how the inputs are related to outputs.

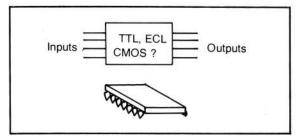

Digital integrated circuits are fabricated on a microscopic scale on wafers of silicon, commonly sealed in oblong, black plastic packages, and connected to the outside world by small metal tabs or pins. The resemblance between the black box idea and digital IC's suggested in Fig. 1-2. is no coincidence. They literally are little black boxes and were designed to be used as such.

Entire circuits, consisting of dozens, hundreds or thousands of components have been packed into them according to strict design guidelines. Because complex circuits have been put into standard, easy-to-handle packages, the user is free to concentrate on the main task of circuit design: how to configure individual chips into a system using the

Fig. 1-2. The IC as black box. In learning about the devices from a functional standpoint, the electronics is incidental.

chips as circuit building blocks. Likewise the student can begin learning about devices and simple circuits by studying digital functions. He does not have to worry about device electronics or electrical characteristics at the outset.

This is the approach taken in Chapters 3 and 4, where the emphasis is placed on what the device does and on the methods used to describe its function.

# DISCRETE COMPONENTS AND DEVICE CHARACTERISTICS

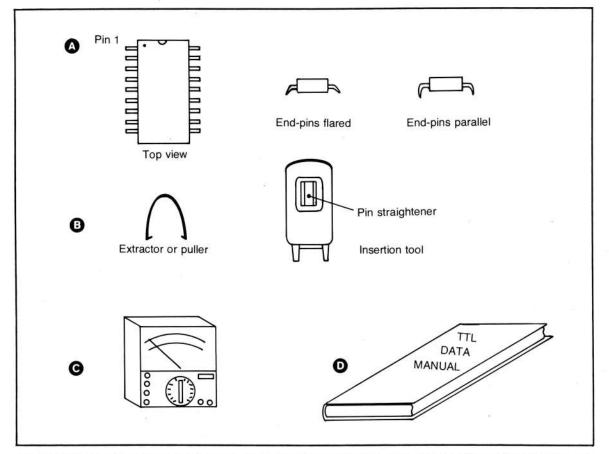

Naturally, the engineer or student will have to take into account a number of practical matters when he actually starts building circuits. Knowledge of power consumption, allowable signal and power supply voltage levels, and current loading limits is essential. What this really boils down to is some working knowledge of basic electronics, at least enough to understand device specifications. But just how much knowledge is enough?

You need only learn about three limited areas: passive elements, the transistor as a switch, and the operation of a typical digital circuit in terms of these individual components.

Passive elements include resistors, capacitors and diodes; the rules governing these components are straightforward. Transistor operation is not as simple. However, we are only concerned with its operation as a switch, not as an amplifier, and this makes the topic much easier. Last, we will look at how these components are configured on a typical IC chip and talk about the IC's *electrical parameters*.

Three chapters—Chapters 5, 6, and 7— are devoted to this material and include supporting ex-

3

periments. These chapters may demand more effort from some of you, especially if you've forgotten or never learned such things as Ohm's Law and Kirchhoff's Law. But remember, the goal is not to turn you into an IC design engineer, but just to teach you some basic electronics.

As a result of your efforts you will be able to open up any IC data manual and read it intelligently. Since the technical data and applications manuals from the many chip manufacturers are valuable information sources in their own right, this is an important skill. The discussion of digital IC characteristics in Chapter 7 includes the type of specifications you would normally encounter in data manuals. Therefore, by the time you finish this section, you should be fairly adept at reading and using them.

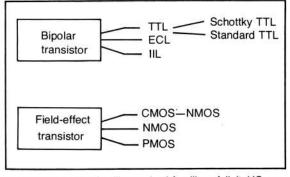

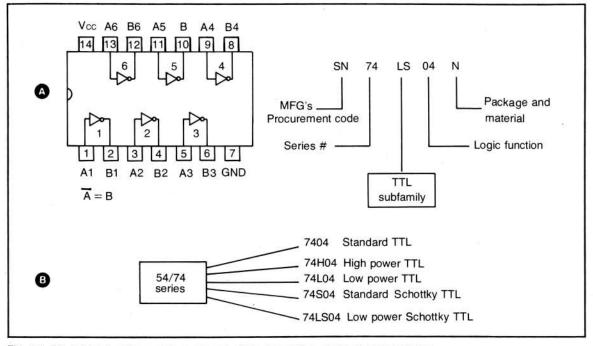

#### FAMILIES AND SUBFAMILIES

The subject of families of IC devices is really an extension of the subject just discussed, discrete component electronics. As mentioned, ICs are the result of rigid design criteria which define the electrical properties of the device packages. IC design also involves building in the black box function; the specific logical, arithmetic or other task that the device is to perform. Obviously you may require that a device fulfill a given function and be able to operate in a wide variety of settings. For instance you may want the fastest device currently available and require the lowest power consumption available. Unfortunately you can get either characteristic alone, but not both combined in the same chip. This is known as the speed/power tradeoff. There are other tradeoffs as well.

In other words, whatever property you care to discuss—noise immunity, power use, cost, current output, operating temperature range, speed, etc.—you will have to make compromises. Improvement in one factor is usually realized to the detriment of one or more of the others.

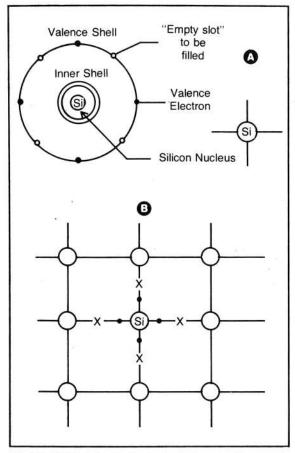

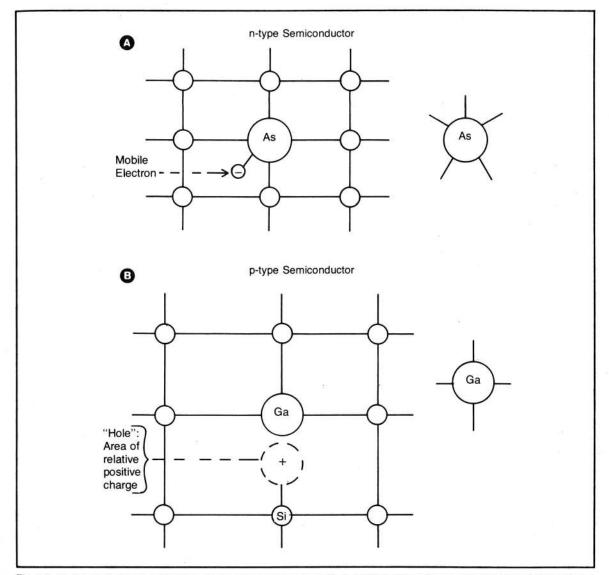

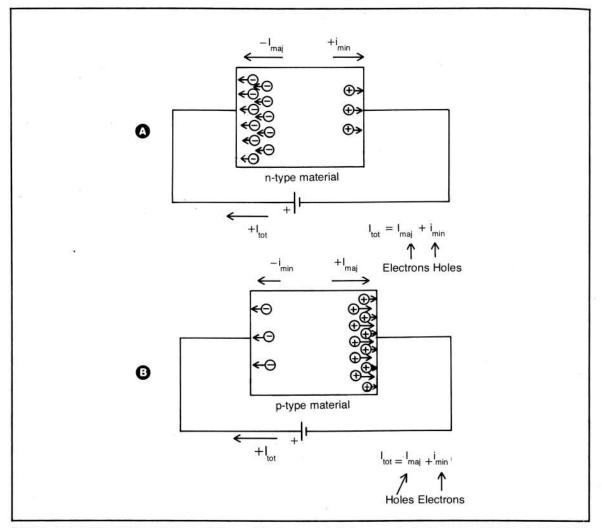

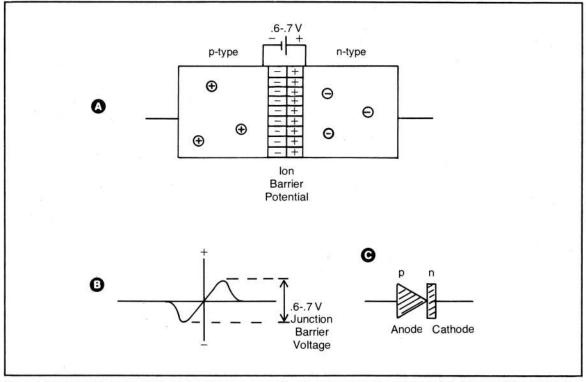

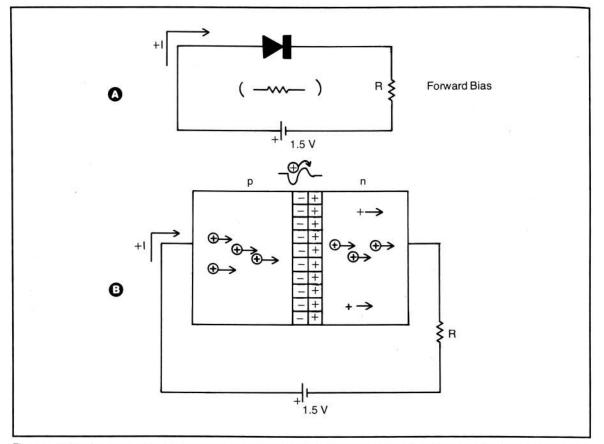

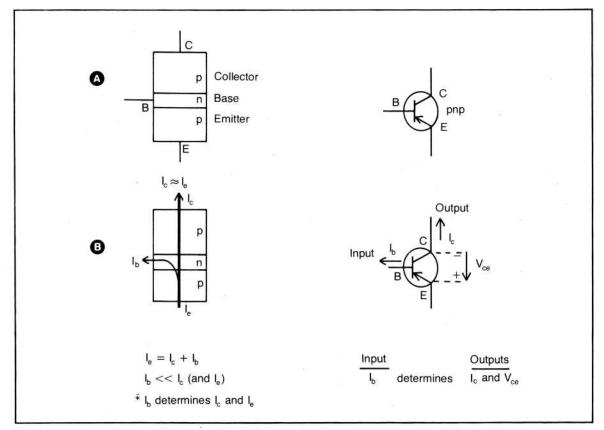

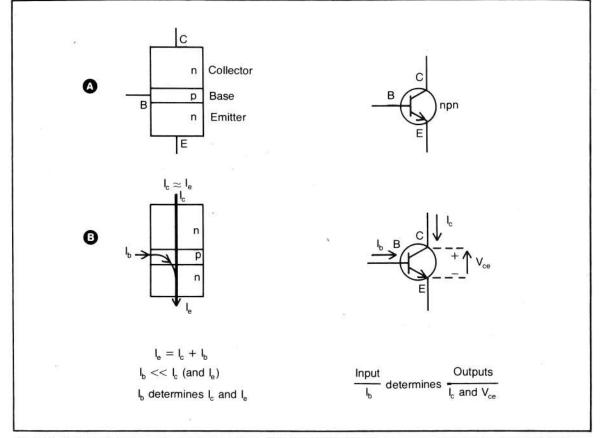

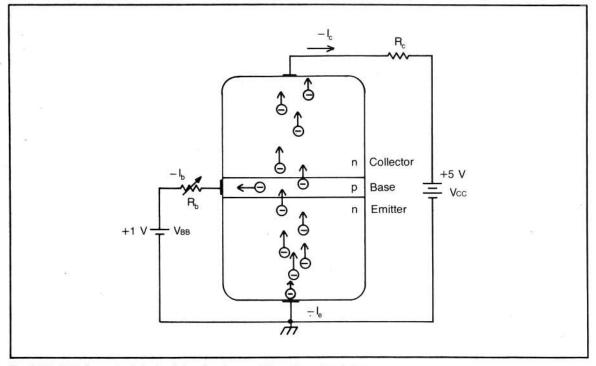

The reason for these real-world constraints involves the type of semiconductor used to make the device as well as the fabrication method employed. The nature of your compromise is very much determined by the *family* of IC device that you choose. Most devices fall into either one of two broad semiconductor families: those based on the *bipolar transistor* and those based on the *field-effect transistor*. See Fig. 1-3.

Fig. 1-3. The major families and subfamilies of digital ICs are based on the two main types of transistor. The electronics is important when it comes to actually building the physical circuit.

The bipolar transistor, the original one invented in 1948, is the basis for a major family called *transistor-transistor-logic*, or *TTL* for short. Other bipolar IC families are *ECL* (emitter coupled logic) and *IIL* (integrated injection logic). Each is the result of careful consideration of user requirements and of fabrication techniques. Each has it's own strengths and weaknesses. For example, both ECL and TTL are used in digital logic applications. ECL is lightening fast, but also power hungry, and very demanding of precise power supply voltages. TTL is also fast, though not so fast as ECL. However, it uses less power and is less finicky in regard to supply voltage.

Integrated injection logic, the other major bipolar family, is used in linear applications. TTL and ECL are primarily digital devices. Linear IIL devices include oscillators, voltage to frequency converters, modulators, and amplifiers. This family will not be considered further.

The other major family of IC is based on the field effect transistor, which operates on slightly different principles than the bipolar transistor. The various device types in this group are collectively known as *MOS* devices, metal oxide on silicon.

MOS family names refer to the type of semi-

conductor, positive or negative type, used in the given family. In *PMOS*, the charge carriers are positive (holes). In *NMOS*, the charge carriers are negative (electrons). In *CMOS*, (complementary MOS), field effect transistors made from both types of semiconductor are used. CMOS also has high performance cousin HCMOS.

At this stage, the important thing to keep in mind about MOS ICs is that they use very little power in comparison to TTL and are proportionally slower. In particular, the CMOS family (complementary MOS) consumes only a fraction of the power of comparable TTL devices, making CMOS very useful in battery powered applications where high speed is not essential. A second major advantage of CMOS over TTL is that you can safely use a wide range of power supply voltages.

However, all MOS devices have a handling problem: they are inherently sensitive to static discharge. Older CMOS versions required that the user be attached to earth ground via conductive floor mats and wrist straps, and that he observe certain storage and handling precautions when working with these ICs. If you rub your feet on a carpet on a dry winter day and then touch a metal object, you will have a clear idea of how static discharge can destroy a delicate MOS chip. This problem has been partially remedied in more recent designs. However, it is still possible to destroy one of these chips with static electricity if you don't follow these precautions.

Where does all this leave us in terms of choosing the best family on which to learn?

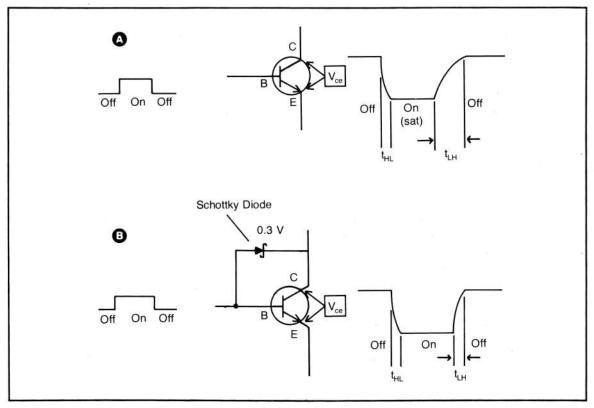

Well, there is a subfamily of TTL which meets the student's and the experimenter's needs admirably that is called *low power schottky ttl* (LSTTL). LSTTL devices are based on the Schottky design enhancement of the traditional bipolar transistor. Schottky transistors are faster yet conservative of power. This means that LSTTL devices enjoy an excellent combination of both high speed and modest power drain. At the same time, they have an edge over CMOS in terms of ruggedness and are also a bit cheaper than CMOS. Because of these last factors, LSTTL has been chosen for the experiments in this book.

Table 1-1 provides a quick comparison of CMOS and LSTTL, and covers the points just mentioned.

# SCALES OF INTEGRATION

Scale of integration refers to the number of components that can be packed onto a unit area of semiconductor. The number of transistors per square millimeter of silicon would be an example. In practice chip density or *scale of integration* relates to the finished IC package as you see it on the shelf. The more components that manufacturers can miniaturize and integrate in a given area, the higher the scale of integration.

| Characteristic                                                                     | LSTTL      | CMOS           |

|------------------------------------------------------------------------------------|------------|----------------|

| Power Supply Voltage Range<br>(in volts)                                           | +4.5 - 5.5 | +3.0 - 15      |

| Power Consumption per Gate<br>(in milliwatts mW)                                   | 1.0        | .011           |

| Speed or Propagation Delay<br>(in nanoseconds ns, i.e.,<br>billionths of a second) | 10         | 100 - 150      |

| Ruggedness<br>(in handling)                                                        | excellent  | satisfactory * |

| Cost                                                                               | low        | low - moderate |

| Noise Immunity                                                                     | good       | very good      |

Table 1-1. Some Typical Device Characteristics for Two Popular IC Families.

CMOS demands certain handling precautions, is more sensitive to static discharge and to improper input currents.

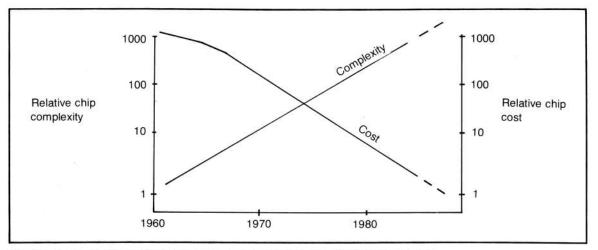

Fig. 1-4. The growth of IC complexity or scale of integration in the past two decades.

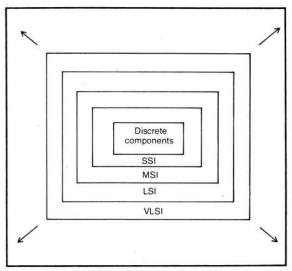

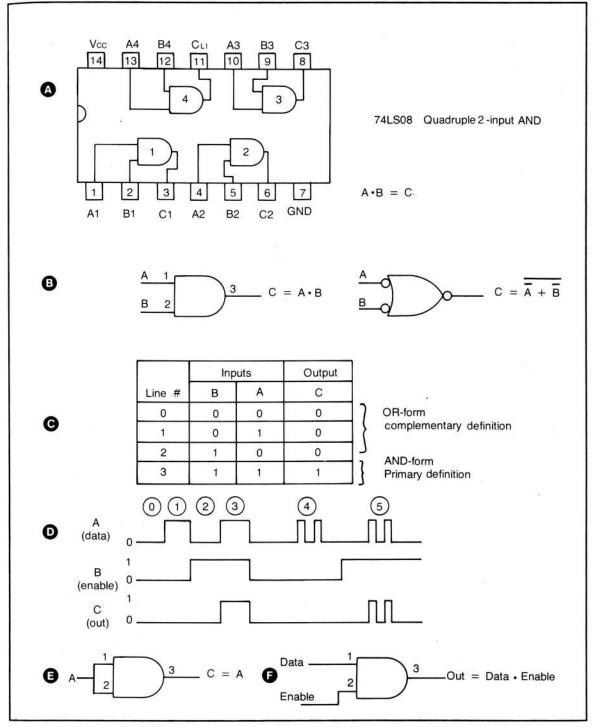

Referring to Fig. 1-4 and Fig. 1-5 and to Table 1-2 you can see that *small scale integration* devices (SSI) made their appearance around 1960. They have, by definition, less than 100 transistors per IC device. (The term *device* means the functional unit on the chip: a flip-flop or a gate for instance). The smallest logic element is a circuit composed of transistors, resistors and diodes, often called a *gate*. A typical gate contains from 5 to 9 transistors. The gate count per device is more meaningful than the number of transistors per device. Hence, SSI IC devices are usually defined as having a maximum of 11 gates.

In the mid to late 1960's, *medium scale integration* (MSI) became available. Digital ICs at this level ranged from 100 to 1000 transistors or 12 to 100 gates per digital device. MSI devices provide many of the workhorse functions of digital circuits: counters, registers, decoders, etc.

Large scale integration (LSI) is defined as having from 100 to 1000 gates, or up to 10,000 transistors per device. More recently, VLSI (very large

Fig. 1-5. The rise of IC complexity has been accompanied by dramatic decreases in cost.

| Scale of<br>Integration | Approximate Time Of<br>Introduction | Transistors<br>Per Chip | Gates<br>Per Chip |

|-------------------------|-------------------------------------|-------------------------|-------------------|

| VLSI                    | 1980                                | > 100,000               | > 10.000          |

| LSI                     | 1970                                | 1000 - 100,000          | 100 - 1000        |

| MSI                     | 1965                                | 100 - 1000              | 12 - 100          |

| SSI                     | 1960                                | < 100                   | < 12              |

Table 1-2. Number of Transistors and Gates Per IC Device as a Function of the Scale of Integration.

scale integration) came into being. VLSI can contain up to 10,000 gates or 100,000 transistors per package. Ultra Large Scale Integration is also in the works. It will contain up to 1 million transistors per device. LSI, VLSI and ULSI are exemplified by microprocessor chips and by large (64-bit and 256-bit) computer memory.

The whole point can be summarized in one sentence. Impressively complex functions, in ridiculously small packages are available at astoundingly low cost.

As one ascends the scale of integration, one sees more and more complex and sophisticated functions. Cost has dropped off dramatically as the complexity has risen. These changes have been exponential. The cost of computer hardware is decreasing by a factor of about ten every seven years or so. Your two or three thousand dollar desk-top system of today would have carried a price tag in 1960 of close to a million dollars for equivalent functions and with consideration for space, power and maintenance figured in.

Another way to view this phenomenally rapid development from the black box perspective is suggested in Fig. 1-6. In the pre-1960 days, circuits were built largely from individual electronic components. Since then there have been a series of major steps in which the prior technological scale was condensed and integrated into a denser and more complex black box. In this sense, the digital system designer may not care about the MSI level functions that have been packed into the VLSI microprocessor chip that he is working with. He simply uses this chip as a functional black box, along with many other black boxes, in the digital system he is creating.

Despite these advances, the lowly SSI device

still occupies a very important place. As we'll see later, SSI chips serve as a sort of glue which holds the more complex chips together. Occasionally, some simple circuit functions are best realized entirely by SSI chips rather than by higher level devices.

The educational role of SSI is equally as important as their design role. Understanding SSI is straightforward because of its relative simplicity. You can examine the outsides of SSI chips and understand all of the basic digital logic functions. You can also examine their insides and learn the basis for their electrical characteristics and how to use them in practical circuits. Further, once you master SSI, MSI components present no real difficulty, because they are just extensions of the SSI building block functions. Subjects that fall into the LSI range, such as microprocessors, memory, in-

Fig. 1-6. The black box of today is swallowed by the next larger scale of integration of tomorrow.

terfacing and computer hardware applications are then quite accessible.

# BINARY AND HEXADECIMAL NUMBERS

You should have some familiarity with binary and hexadecimal number systems at the outset. An ability to translate a number in either system to its decimal equivalent is all that is really required, so the following will be brief.

The simplest and hence most reliable number system is the binary number system. In this system there are only two values for each digit: 0 and 1. Numbers in this system are based on the power of two, rather than on the power of ten, as in the familiar decimal system. Binary is said, therefore, to be a *base-two* system.

Binary is ideally suited to digital circuits for one main reason: lack of ambiguity. In digital circuits, the circuit elements can assume only one of either of two states or values. Such a circuit element can be either on (conducting) or off (nonconducting). This is analogous to a mechanical switch being closed or open. In fact, the basis for all digital circuits is nothing more than an electronic version of the mechanical switch. In short, because there are no intermediate values between high and low, 0 and 1, or on and off, digital systems are by their nature, very, very reliable. (This is unlike analog circuits, which operate on a continuum of values, with the exact state of the circuit element always approximate, always slightly uncertain).

In digital circuits, the binary values of 0 and 1 correspond to two different voltage levels: high and low. These two levels are called *logic high* and *logic low* because they represent the two logical states: true and false. In the LSTTL logic family the nominal values of these two voltage levels are 0 and +5 volts for 0 and 1, respectively. (There is actually a range for valid logic low/0 and logic high/1 voltage levels, something detailed later on.)

# **Binary Representation**

Let's formalize a little. A **bit** is a single digit in the binary number system. It can assume the values of 0 and 1, just as a decimal digit can assume a value in the range of 0 to 9. Just like decimal digits, binary digits or bits have a *place value*. For instance, in the number 539, the place values are from right to left: units, tens and hundreds. More generally, the place values are 1, 10, 100 and so on, proceeding by a factor of 10 for each place to the left. The leftward most digit is the most significant digit, or MSD, because it has the highest place value or numerical weight.

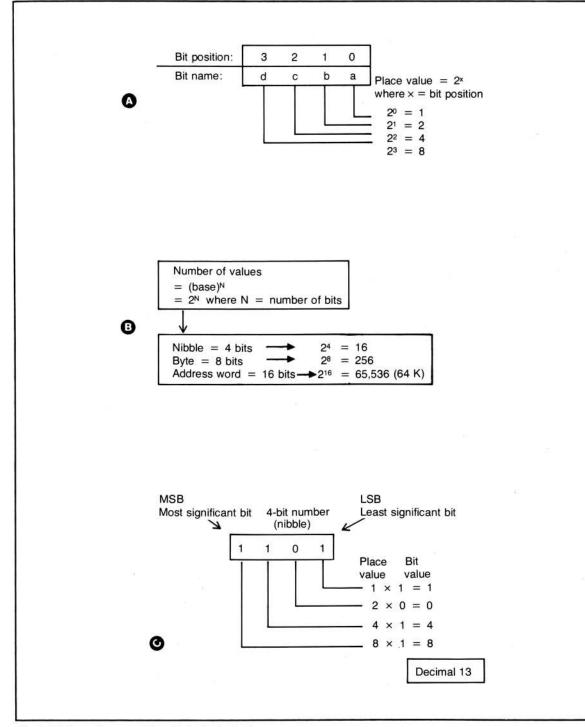

How this works out for the binary number system is illustrated in Fig. 1-7. A four bit binary number is given in Fig. 1-7A, with the places called d, c, b, and a from most to least significant bit. The positions for these bits are numbered 3, 2, 1, and 0 respectively. Since this is a base-two number system, the place value for each position is given as:

Place Value =  $2^x$  where x is the bit position.

That is, the place values in the binary scheme are, from right to left, 1, 2, 4, 8, and so on by powers of 2.

The number of values represented by a certain number of bits can be figured out quite easily. You know that a three digit decimal number can assume any one of 1000 values when you include 0. This is just 10<sup>3</sup>: you simply raise the number base by the number of digits. In binary, this becomes:

Table 1-3. Equivalence of Binary, Decimal, and Hexadecimal (see text).

| Decimal               | Binary | Hexadecima       |

|-----------------------|--------|------------------|

| 0                     | 0000   | 0                |

| 1                     | 0001   | 1                |

| 1<br>2<br>3<br>4<br>5 | 0010   | 2                |

| 3                     | 0011   | 3                |

| 4                     | 0100   | 2<br>3<br>4<br>5 |

| 5                     | 0101   | 5                |

| 6                     | 0110   | 6                |

| 7                     | 0111   | 7                |

| 8                     | 1000   | 8                |

| 9                     | 1001   | 9                |

| 10                    | 1010   | A                |

| 11                    | 1011   | В                |

| 12                    | 1100   | С                |

| 13                    | 1101   | D                |

| 14                    | 1110   | E                |

| 15                    | 1111   | F                |

Fig. 1-7. Binary Representation. Refer to the text.

9

Number of Values =

$$(base)^{N}$$

where

N = number of bits

or

Number of values =  $2^{N}$

This works out to 16 values (0 to 15 decimal)for a four bit number or *nibble* and to 256 values for an eight bit *byte*. See Fig. 1-7B. For a 16-bit number, there are  $2^{16}$  possible values, or 65,536-64 K for short (1024 bits = 1 K). This 16-bit length is known as an *address word* in the typical 8-bit microcomputer.

You can work out the decimal equivalent of any binary number using the method shown in Fig. 1-7C. Take the bit value (0 or 1) of each bit position and multiply by the corresponding place value; then add the result.

Table 1-3 lists decimal numbers with their binary equivalents. The range of values for a four bit number are given. The table also indicates that you can represent a binary nibble with an alternative number system, which has a base of 16. This is the hexadecimal system with which you may be familiar.

Fig. 1-8. Hexadecimal representation. Refer to the text.

#### **Hexadecimal Representation**

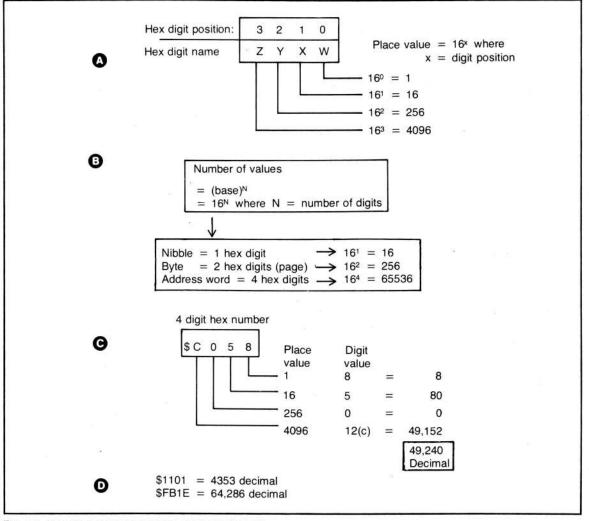

The reason for using the *hexadecimal* number system is simple: there is a nice symmetry between the binary system and the hexadecimal form of representation. Each 4-bit nibble in binary can be represented by a single hex digit. This is demonstrated in Table 1-3. As a convenience, you should think of the hex system as merely a condensed form of binary.

Following the same sequence as we did for binary, refer to Fig. 1-8. Again, each digit in a hex number has a position number and a position name. In this four digit number (Fig. 1-8A), we call the digits Z, Y, X, and W. The digit positions are 3, 2, 1 and 0. The place values are given by 16<sup>x</sup>, where x is the digit position. Digit Z in the 3-position has a place value of 4096, etc.

Figure 1-8B shows that a four digit hex number can assume 65536 different values, the same as a sixteen bit binary number, certainly an improvement in economy of representation. A single hex digit—with values 0 to F hex, or 0 to 15 decimal—is equivalent to a four bit binary number. Two hex digits are equivalent to a byte, and four hex digits to a 16-bit address word.

Figure 1-8C illustrates the conversion of a four digit hex number to its decimal equivalent by the same process as that for binary to decimal conversion. Note that hex numbers are preceded by a dollar sign \$. This number, \$C058, happens to be the memory address of annunciator 0 off the Apple game port (explanations later).

Finally, Fig. 1-8D shows the decimal equivalent of two other hex numbers. Verify them for yourself. The first looks the same as the binary example in Fig. 1-7C except for the preceding \$ sign. The second number happens to be the address in the Apple Monitor for reading the paddles off the game port.

# **The Digital Desktop Laboratory**

In the last chapter, we took a broad view of digital electronics and the key role the individual IC devices play in the learning process. By now, you are probably anxious to start doing something; therefore, in this chapter you'll be shown how to set up the computer-based logic trainer. You'll also collect a few other items which, together with the trainer will comprise a desktop laboratory for studying digital devices and circuits.

First, let's look at the Apple game port.

# THE GAME PORT CONNECTION

The logic trainer could be built around one of the peripheral slots on the Apple main board. With all those signals (48 to be exact) a really elaborate trainer/prototyping setup would be possible. However, slot-based input/output (I/O) projects such as these are not for the beginner. They require knowledge of interfacing, construction methods and troubleshooting, and a fair cash investment for materials and equipment.

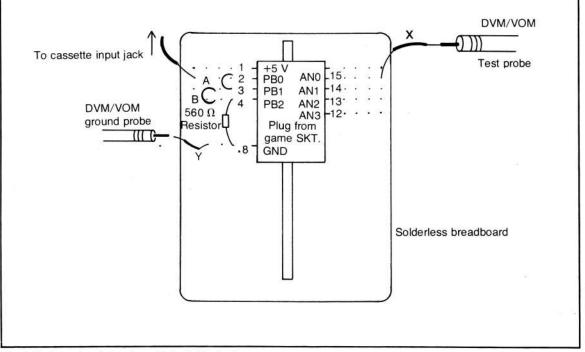

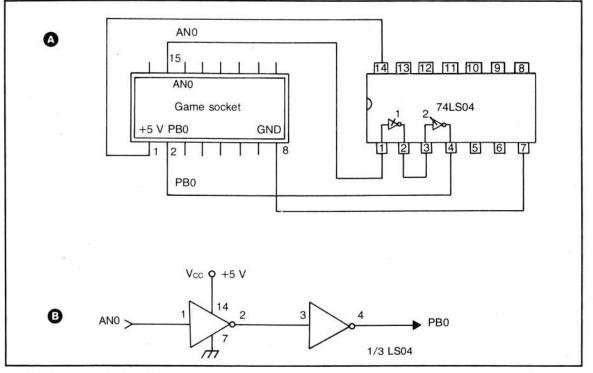

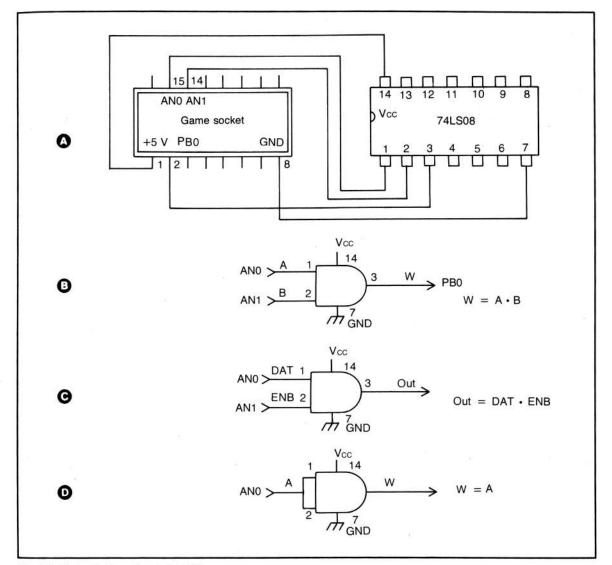

However, the Apple game port provides the

cheapest, easiest and most immediate approach to setting up the computer-based logic trainer. It is well suited to its role because of the number of signal lines available on its socket. There are 12 signal lines plus power and ground. These are quite adequate for our logic trainer/breadboard system as well as for a number of other applications such as A/D conversion.

In short, a system based on the game port is the ideal choice for the beginner. It will give you all the necessary features of the traditional stand-alone trainer, plus the advantages of a dynamic tv monitor display of your experiments, but without the expense and experience needed for the elaborate slot-based system.

As you advance in digital electronics, you may find a need for a conventional trainer/breadboard because they are handy when several projects are going on simultaneously. Later, more sophisticated projects which require the peripheral slot signals may attract your attention. But for an outlay of 20 dollars and half hour or so to type in the utility program, you're ready to start experimenting.

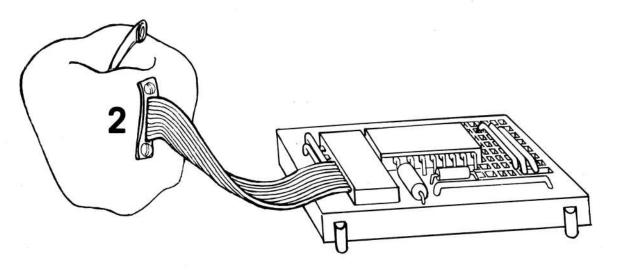

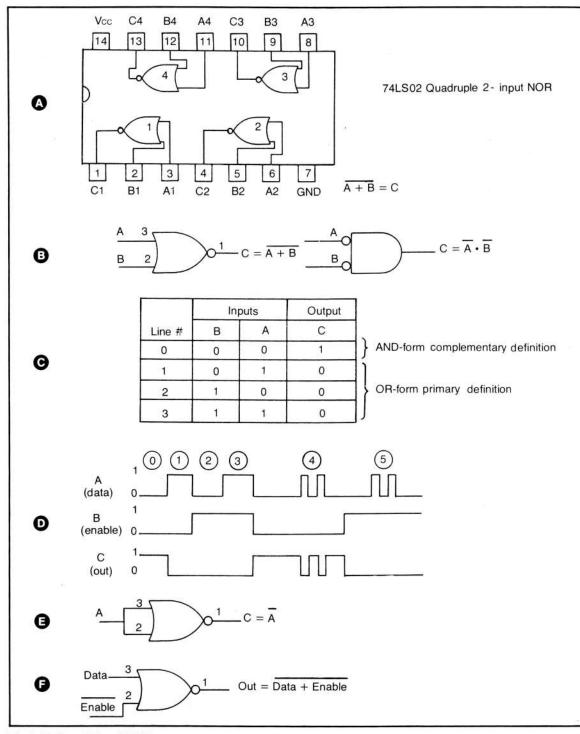

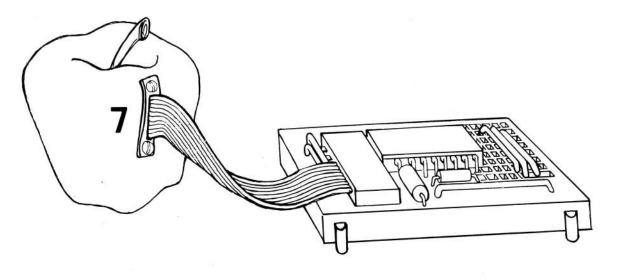

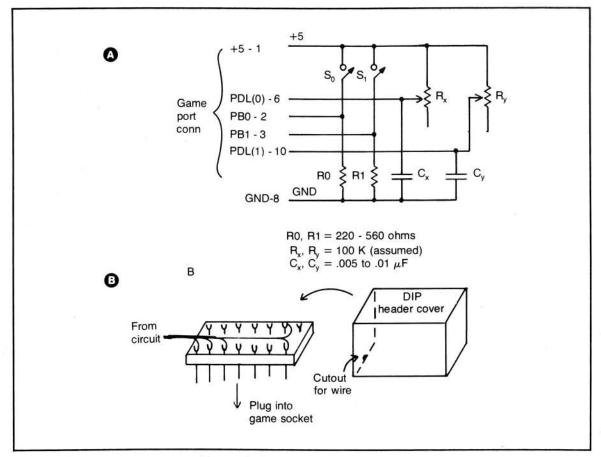

Fig. 2-1. Game socket pin-out.

## **Game Socket Overview**

The hardware/mechanical part of setting up the trainer involves nothing more than plugging one end of a DIP (dual-in-line-package) jumper cable into the game socket and the other end into a small breadboard strip. Before doing this, you should be very familiar with the port signal lines you will be using.

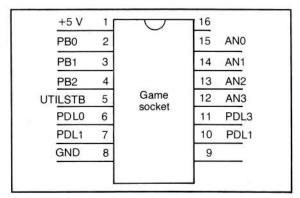

Figure 2-1 is a view of the 16-pin game socket located at the upper right hand corner of the Apple main board. Table 2-1 is a listing of all of the digital game port signals: their pin numbers, names, labels, locations in memory, and function. Also listed is the cassette input.

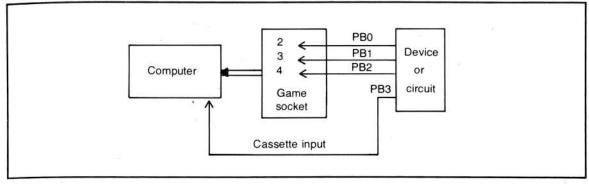

For the trainer you will require four outputs, four inputs, and power and ground. The four annunciator lines are 1-bit digital (on or off) outputs from the computer; these will serve as inputs to the device or circuit under study. You also need four single bit lines into the computer in order to read the outputs from the device or circuit. These are the three pushbutton lines plus the single cassette

Table 2-1. Game Port Signals, Including the Cassette Input, Used In the Computer-Based Logic Trainer. BDIS Also Uses the Utility Strobe. Paddle (Analog Game) Inputs Are Also Present. These Lines are Detailed Later on.

| Pin          | Pin Signal Name   |       | Label Address |         | Function                                                   |  |

|--------------|-------------------|-------|---------------|---------|------------------------------------------------------------|--|

|              |                   |       | Hex           | Decimal |                                                            |  |

| 15           | annunicator 0 Off | AN(0) | \$C058        | 49240   | Output                                                     |  |

|              | annunciator 0 On  | AN(0) | \$C059        | 49241   | Output                                                     |  |

| 14           | annunciator 1 Off | AN(1) | \$C05A        | 49242   | Output                                                     |  |

|              | annunciator 1 On  | AN(1) | \$C05B        | 49243   | Output                                                     |  |

| 13           | annunciator 2 Off | AN(2) | \$C05C        | 49244   | Output                                                     |  |

|              | annunciator 2 On  | AN(2) | \$C05D        | 49245   | Output                                                     |  |

| 12           | annunciator 3 Off | AN(3) | \$C05E        | 49246   | Output                                                     |  |

|              | annunciator 3 On  | AN(3) | \$C05F        | 49247   | Output                                                     |  |

| 2            | pushbutton 0      | PB(0) | \$C061        | 49249   | Input                                                      |  |

| 3            | pushbutton 1      | PB(1) | \$C062        | 49250   | Input                                                      |  |

| 4            | pushbutton 2      | PB(2) | \$C063        | 49251   | Input                                                      |  |

| rear<br>jack | cassette in       | PB(3) | \$C060        | 49248   | Input                                                      |  |

| 1            | +5 volts          | Vcc   | N.A           | ι.      | Nominal limit of 100mA current drain on this power supply. |  |

| 8            | ground            | GND   | N.A           |         | Circuit ground.                                            |  |

input line. Finally, you need the +5 volt power line and ground. Discussion of the paddle and utility strobe lines will come later, as they are required. Right now, let us consider the required lines in detail.

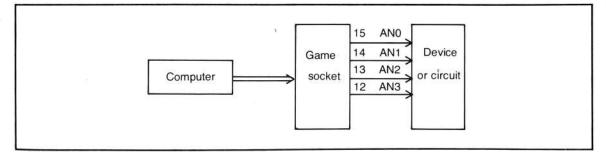

### **Annunciator Outputs**

Figure 2-2 emphasizes the relationship between computer, annunciators and peripheral device. These four annunciator pins on the game socket serve as 1-bit outputs from the computer to the peripheral device. They can assume either of two states: on or off. The on state corresponds to a voltage high or a binary value of 1. The off state corresponds to a voltage low or a binary value of 0. When the annunciators are used to control digital circuits, it is often appropriate to think of these states as binary 1 or 0. Alternatively, they may be viewed as simply on or off, as when they are used to control a lamp, relay or alarm buzzer.

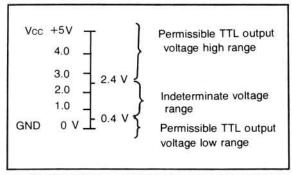

As to the actual voltages on these lines, remember that the annunciators are TTL outputs. This means that during the off/0 state the respective line has a value of near zero volts, and that during the on/1 state the respective line has a nominal voltage of around 4.0 volts. These voltage levels are typical of all TTL devices, both Schottky and nonSchottky.

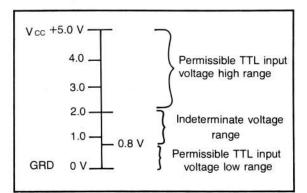

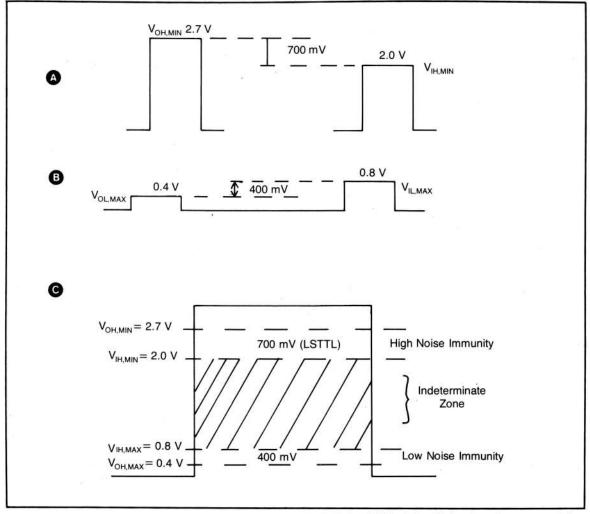

Figure 2-3 indicates that TTL ICs have been designed to give well-defined output voltages. Voltage high is defined as 2.4 volts or more. Voltage low must be between 0 and 0.4 volts. Anything between 0.4 and 2.4 volts is defined as an *indeterminate output* voltage level and would imply either a faulty device or improper use of the device.

Fig. 2-3. TTL output voltage ranges off the annunciator lines.

All TTL subfamilies have been designed to these output specifications, and the annunciator circuitry, being TTL, likewise conforms to them.

Each annunciator is assigned a pair of locations in memory, one to turn it on and the other to turn it off. These locations or addresses in memory are just like switches and may be activated merely by referring to them with the proper command. The BASIC POKE command will do the job, either from within a program (deferred) or as immediate commands issued from the keyboard. Provided that you access the correct address, it makes no difference what value you poke into that address. You can even use a PEEK command. For example:

| POKE 49240,0  | or                |

|---------------|-------------------|

| POKE 4920,137 | or                |

| PEEK (49240)  | will each cause   |

|               | ANN(0) on pin 15  |

|               | to go off or low. |

|               | S                 |

And, POKE 49241,0

or

Fig. 2-2. Annunciator output lines off the game socket.

15

| POKE | 49241,217 |

|------|-----------|

| PEEK | (49241)   |

or will each cause ANN(0) on pin 15 to go on or high.

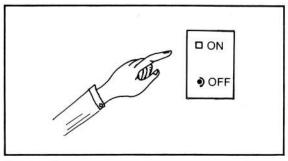

Because you are accessing one of a pair of locations, the action is much like one of the oldstyle two button wall switches shown in Fig. 2-4. Pressing the on button by any means gives you the same end result: the room light turns on. Now press the off button below (which popped out when you pressed on) and the light goes off. The analogy between the two annunciator addresses and the two light switch buttons is very close.

Fig. 2-4. The annunciators are toggled much like wall switches: two separate locations for turning a light on and off.

This is why the annunciator addresses and similar memory locations are referred to as *softswitches*; by accessing these locations from software you can effect a change in hardware. In this case the voltage level changes on a particular socket pin. Because you are referencing one of a pair of addresses assigned to each pin or output line, you are toggling the softswitches.

NOTE: The term *annunciator* can refer to an address in memory, a chip on the main board that holds the high or low voltage, or a particular pin on the game socket. The particular meaning is usually clear from the context. For example, *softswitch* obviously refers to the memory location, while *line* would refer to the actual pin or the wire leading from it to the peripheral circuit. The same distinctions hold true for the pushbutton inputs discussed below.

#### **Pushbutton Inputs**

Figure 2-5 illustrates the three inputs which are usually associated with the pushbuttons found on game controls. The *Apple Reference Manual* refers to these inputs as SW(0)-SW(2) and calls them switches. However, the term pushbutton input conveys the same meaning and is more specific than the term switch. Therefore PB is used as the label in this book.

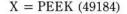

Note that unlike the annunciators, these pushbutton locations are not softswitches because they are computer inputs, not outputs. The computer reads these input lines. Each pushbutton line or socket pin is assigned a single address in memory. This location will contain data indicating whether the line is in a high state or a low state. From BASIC you must use the PEEK command to find out if the voltage is high or low. The form used is:

$x = PEEK (\{address\})$

x = PEEK (49249) for PB(0) for example.

IF x > 127, then the line is high, on, binary 1.

IF x < 128 the line is low, off, binary 0.

x = the value in that address

So much for the addresses and form of command. What about voltages?

The peripheral device connected to the given PB line—whether a mechanical switch or a complex digital circuit—must place the correct voltage on that line. Since the PB input circuitry is TTL, these voltages must adhere to TTL guidelines for acceptable input voltage ranges.

Figure 2-6 depicts these permissible voltages. This diagram is similar to that of Fig. 2-3 except that it refers to TTL inputs, not outputs. Any voltage between 0 and 0.8 volts will be interpreted by a TTL input as a low or 0. Voltages above 2.0 volts are seen as high or binary 1.

Don't get confused about input and output. Just remember that annunciator outputs from the computer may be considered as inputs to a peripheral device under study on the breadboard. Likewise, pushbutton inputs to the computer from a

Fig. 2-5. Pushbutton input lines to the computer.

peripheral may be thought of as outputs from that device or circuit.

**Caution:** If you place a voltage much above +5 V. or much below 0 V. (negative) on the pushbutton inputs to the Apple, the game port circuitry reading these lines could be damaged. Since you are using the Apple's own +5 volt supply off the game port, this caution may seem unnecessary. However, at some time you may advance to a larger external power supply with multiple + and - voltages, so keep this caution in mind.

Naturally, if the peripheral is another TTL circuit, you don't have to worry about voltage compatibility. This is because the maximum allowable TTL output level for a logic low is well below the maximum allowable input level (0.4 and 0.8 volts respectively). Similarly, the minimum allowable output for logic high is well above the minimum allowable input level (2.4 and 2.0) volts respectively). This is the beauty of standardized families and subfamilies, namely compatibility of electrical characteristics. It is generally good practice to stay within the same family unless there are good reasons to the contrary, and this is another reason why LSTTL devices will be used for our experiments.

#### A Fourth Input

It was mentioned earlier that the cassette input could be used as a fourth digital input for monitoring the circuit outputs under study. The physical location for this line is the cassette input jack on the back of the Apple, and is labeled as such. On the Apple *II*e, it is the rightward cassette symbol with the downward-going arrow. On Apple II and II+ it is labeled as IN or as CASS IN. A method which is quick, cheap and compatible with all Apple versions is to simply plug a miniature phono plug (with a single wire attached to the signal lug) into the cassette jack. The other end of the wire is stripped and connected to the peripheral circuit. That's all. There are no traces to cut or main board modifications to be made, so you don't have to be concerned about voiding your warranty.

Like the pushbutton inputs, the cassette input has its own location, as indicated in Table 2-1. To read the status on the cassette line, we use the BASIC command:

Fig. 2-6. Standard TTL input voltage levels.

Because of the circuitry involved, the voltage on the cassette input is inverted, so the corresponding values of high and low are reversed relative to the value of x. That is,

If x > 127 then the line is low, off or binary 0. If x < 128 then the line is considered as high, on or binary 1.

Regarding the voltage levels themselves, there is no problem. The TTL output voltages from the devices being examined are compatible with the linear cassette input circuitry (essentially an IC amplifier called an op-amp).

I am going to call the cassette input pushbutton input 3, or PB(3), as a matter of convenience.

## **Power and Ground**

Five volts at 100 milliamps (mA) current is available on pin 1 of the game socket. This means that you have 1/2 watt or 500 milliwatts (mW) of power to drive your devices or circuits. This may seem small, but it is adequate to power all of the SSI and MSI devices we will be studying, as well as a number of practical circuits consisting of several devices. Ground is on pin 8 of the game socket. Each line is connected to the respective pins on the device(s) being studied. Just remember that you should not short the +5 volt line to ground, or vice versa. If you do, the Apple's self-protecting power supply will emit a clicking sound as it attempts to reset itself by shutting on and off. Turning the machine off and checking for the inadvertant connection between +5 and GND is the best thing to do if this happens. No damage to the machine will result, but do try to avoid this mistake.

There are a few other general precautions to be taken in using the computer-based breadboard. These are mentioned in the introductory section preceding Experiment 1 at the end of this chapter. Disregarding them will do your computer no permanent harm, but do try to adhere to them.

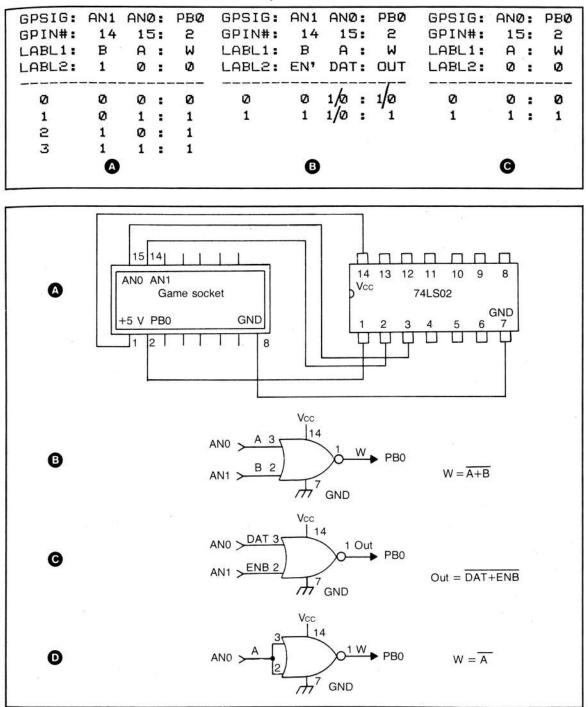

# TURNING THE APPLE INTO A DIGITAL LOGIC TRAINER

Turning the Apple into a logic trainer involves a few inexpensive hardware items by which to externalize the gameport and cassette input signals, plus a utility program, the Breadboard-In-Software (BDIS). These are described below.

# Hardware Hookup

Making the physical connection to the game socket and cassette input jack is simple. Any Apple system which has Applesoft in RAM or ROM is sufficient. Even an INTEGER machine with 16 K of memory an Applesoft in ROM will do. (Are there any left out there?) Besides the Apple, you will need these items:

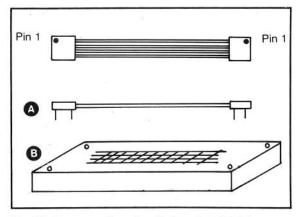

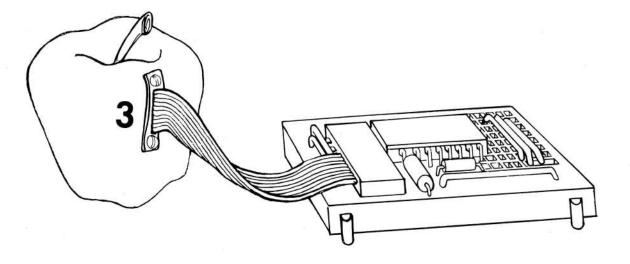

□ A three foot 16-conductor ribbon cable with 16-pin DIP plugs on either end.

□ A solderless breadboard strip.

$\Box$  A miniature phono plug and some solid hookup wire (20 gauge preferred).

Figure 2-7A illustrates the jumper cable. It consists of a length of Insulated Displacement Connector (IDC) ribbon cable, with an IDC DIP plug at either end. The term IDC refers to the mechanical arrangement of contacts in the plugs which makes the close packing of parallel conductors possible. IDC is an industry standard arrangement for jumper assemblies used in digital systems, both at the breadboard and finished product stage. You will find literally hundreds of cable and jumper arrangments advertised in the catalogs for virtually every application. Typically, the pins of the end connectors in

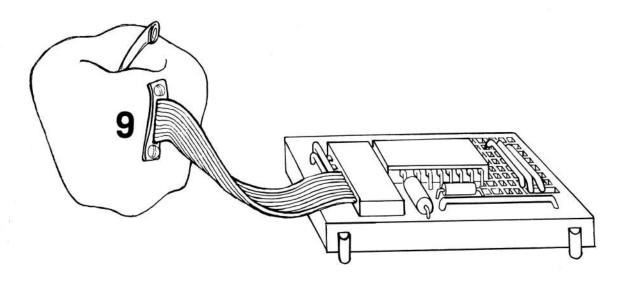

Fig. 2-7. Jumper cable and solderless breadboard.

the IDC standard, be they DIP plugs or some other type, are spaced one-tenth inch apart. (Pin 1 on the plug is indicated by the little dot in Fig. 2-7A).

This 0.1 inch standard is followed in many of the solderless breadboards commonly available, one of which is shown in Fig. 2-7B. The socket holes on these prototype boards are also on 0.1 inch centers and readily accept IC DIP packages and plugs as well as single wires. The DIP devices and connectors simply straddle the center channel in the breadboard. Since each row of five socket holes on either side of the channel are connected in common, you have four remaining holes on the side of each pin available for connections.

To keep matters simple, we will be using a widely available dual-ended 16-conductor jumper, manufactured by A P Products, and a particular breadboard strip, the Experimenter 300 manufactured by Global Specialties. The breadboard was chosen because of cost and availability, but more specifically for its expandability: there are interlocking lips on all four sides of the unit which make the addition of extra units literally a snap.

These items can be obtained from most any electronics parts distributor, either locally or by mail order. I've listed the cheapest sources I could find for these items:  $\Box$  The 3 foot, 16-conductor ribbon jumper cable can be obtained from

Jameco Electronics 1355 Shoreway Road Belmont, CA 94002 PHONE: 415-592-8097 Part # DJ16-3-16 \$3.59 in 1983 catalog, page 25.

Jade, Digi-Key, Active Electronics and A P Products are other sources.

□ The solderless socket strip, or experimenter's protoboard is available from any Radio Shack outlet as well as through mail order.

Radio Shack carries the Experimenter 300 protoboard under Part # RS 276-174 for \$11.95.

□ The miniature phono plug is also available from Radio Shack under Part # RS 274-286@2 for \$1.29.

If you want to purchase one of the game port expanders (see Creative Computing, Sept. 82 for a comprehensive review), you will have the added flexibility that several externalized game sockets afford. They typically run from about \$20 up to \$50 for the more elaborate versions. However, you will still need the DIP jumper, breadboard and phono

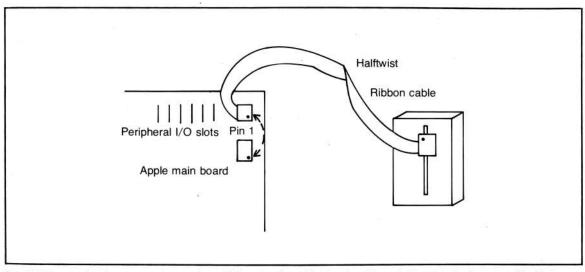

Fig. 2-8. Connecting the game socket on the main board to the solderless breadboard strip using the jumper cable. Make sure pin 1 lines up as shown at either end.

plug listed above for the experiments in this book. So unless you have the urge to play games at a moment's notice, these expanders are not necessary for our purposes.

Now, follow these steps closely. Figure 2-8 shows how the ribbon jumper is connected. With the cover off, you can locate the game socket at the upper right-hand corner of the Apple main board. Note that pin one of the game socket is at the lower right corner of the socket as you look down from the front of the machine. When you insert the DIP plug at one end of the jumper, **Take care that pin #1 of this plug is aligned with pin 1 of the game socket**! A half twist in the cable will be necessary to align pin 1 as indicated in the figure.

Now lead the jumper out of the back panel slot of the Apple (or through a panel cutout in Apple IIe) and replace the cover. Plug the other end of the ribbon cable into one end of the breadboard strip as shown in Fig. 2-8. This time the 1 pin of the DIP plug will be oriented to the upper left, with the plug straddling the center channel of the breadboard, as illustrated.

Finally, take a 2½ to 3 foot length of solid 20 gauge hookup wire and strip about ½ inch of insulation off each end. Unscrew the phono plug cap. Pass one bare end of the wire through the tip of the lug hole (or wrap the bare end if there is no hole) and solder it as shown in Fig. 2-9. Crimp the lug teeth around the insulation and screw the cap back on. Then plug the phono plug into the cassette input jack at the back of the Apple. You can put the other bare end of the lead wire into an empty hole on the solderless protoboard if you desire.

### The Breadboard-In-Software Program

Every logic trainer has to fulfill the following basic functions:

$\Box$  Send digital signals to a device or circuit under examination.

$\Box$  Receive signals from the circuit.

$\Box$  Display those signals.

The conventional, stand-alone logic trainer has slide or toggle switches to send highs or lows to the circuit. These inputs to the circuit or device are indicated by the physical position of the switches. Light emitting diodes (LEDs) usually serve as indicators for the circuit outputs. The only way of recording the various states of inputs to and outputs from the circuit is by paper and pencil. One must be sure that the right switch position and the right LED condition correspond to the right column of data you are writing on. This method of keeping track of experiments can be rather laborious to say the least. It can take a bit of the fun out of working with the hardware.

In the computer-based trainer, things are much easier. The keyboard digits replace the toggle switches, and the tv or video monitor replaces the simple row of LEDs. With a computer generated display of our experiments, the work of examining device and circuit operation is almost a pleasure when compared to the conventional approach. Both inputs and outputs are echoed to the screen in a convenient, easy to read format, one which you can modify as appropriate. You are able to use meaningful headings, such as IC pin-outs and signal

Fig. 2-9. Details of the cassette input jack with attached lead wire.

| DIP Jumper            | A three foot, 16-conductor ribbon cable with<br>16-pin DIP plugs at either end. Used to<br>externalize the game port signals.                                                                                                       |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       | A P Products 924116-36                                                                                                                                                                                                              |

| Solderless Breadboard | Usually, a rectangular plastic object with many<br>small socket holes or "tie points" for the<br>connection of wires and components. Cheap and<br>reusable. A boon to the experimenter and<br>circuit designer. Global Specialties: |

| Miniature Phono Plug  | Experimentor-600<br>Used to input signals into the "fourth<br>pushbutton" line, the cassette input.<br>Any local or mail order store.                                                                                               |

Table 2-2. The Three Hardware Items Needed to Turn the Apple Into a Digital Logic Trainer.

names, both as an aid in double checking the wiring, and in interpreting the final results. In fact, you will be able to generate a table of results and print them out for a permanent record of your experiments.

All of these features are provided by the Breadboard-In-Software utility program, and are further outlined in Table 2-2. Each is explored in detail in Experiment 1 at the end of this chapter. As you begin using BDIS, you will discover that it has something of the feel of a simple video game, or more accurately of a simple spreadsheet program.

BDIS, the brain of the trainer, is written mostly in Applesoft BASIC as you can see from

Listing 2-1. A short Keyread machine-language subroutine is also necessary to monitor keyboard input and to aid in continual updating of the display. This is given in Listing 2-2. I'll talk about entering the listings in a moment.

BDIS was written in a structured manner. Most of the code is devoted to parsing using input, formatting the display, reconfiguring the display, and enable printout. Only three lines of code are actually devoted to toggling the annunciator outputs and reading the pushbutton inputs. The program will run on any standard Apple: the II with A/S (Applesoft) in ROM, on a II+, and on a *II*e in the

| our Line Heading   |             | Two are user definable for meaningful signal<br>names, pin-out designations, etc.                                             |  |  |  |

|--------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Tabular Display    |             | Up to four inputs and four outputs displayed to<br>the screen. Format can be reconfigured by the<br>user.                     |  |  |  |

| Automatic Line Nun | nbering     | Each entry line is numbered. This feature is<br>especially convenient when studying such devices<br>as counters and encoders. |  |  |  |

| Commands           | Number Keys | - for toggling the annunciators on and off.                                                                                   |  |  |  |

|                    | Return      | <ul> <li>to generate a new entry line and "truth tables".</li> </ul>                                                          |  |  |  |

|                    | Ctrl-H      | - to clear the screen (HOME).                                                                                                 |  |  |  |

|                    | Ctrl-R      | - to reconfigure the screen display (see Experiment 1).                                                                       |  |  |  |

|                    | Ctrl-P      | - to "dump" the screen display to a printer.                                                                                  |  |  |  |

|                    | Ctrl-Q      | - to quit BDIS.                                                                                                               |  |  |  |

| Compatibility      | "S"         | - to trigger the utility strobe, pin 5                                                                                        |  |  |  |

| Compatibility      |             | Apple II with Applesoft in ROM, II+ or I/e.                                                                                   |  |  |  |

|                    |             | Apple I/e owners should have the 80 column card<br>turned off before running the program.                                     |  |  |  |

Table 2-3. The Main Features of the Breadboard-In-Software (BDIS, C. 1984).

10 15 REM BREADBOARD IN SOFTWARE 20 REM BDIS - VERSION 1.1 25 REM COPYRIGHT 1984 30 REM CHARLES ENGELSHER 35 36 REM 37 REM PRINT CHR\$ (12); CHR\$ (21); REM CTRL-L&U TO HOME AND DEACTIVATE 80 40 COL CARD ON JEE. 50 POKE 33, 40: REM IN CASE YOU'VE BEEN EDITING WITH POKE 33, 33. PRINT CHR\$ (4);"BLOAD READKEY, A\$300" 60 100 REM 101 MAIN ((((((( 102 REM 105 HOME : VTAB 10: HTAB 9: PRINT "BREADBOARD IN SOFTWARE" GOSUB 1010: GOSUB 1200: REM INITIALIZE & PRINT HEADINGS. 110 VTAB 5: GOSUB 5015: REM NEXTLINE 120 200 CALL 768:KY = PEEK (6):TS = SW: REM READ KEYBOARD & STORE PRIOR SW VALUE. IF KY = 0 THEN GOSUB 3010: GOSUB 4020: GOTO 200: REM CONTINUE UPDA 205 TING PUSHBUTTON DISPLAY UNTIL A KEY IS PRESSED. 210 SW = KY - 48: IF (SW = ) 0) AND (SW ( = NAN) THEN GOSUB 2010: GOSUB 3010: GOSUB 4010: GOTO 200: REM IF SW VALUE IS LEGAL. 215 SW = TS: REM IF NOT, RESTORE PRIOR (LEGAL) SW VALUE. 220 IF KY = 13 THEN GOSUB 5010: GOTO 200: REM 'CR'...NEXTLINE 230 IF KY = 17 THEN GOTO 900: REM Q^ ... QUIT 240 IF KY = 8 THEN HOME : VTAB 5: GOSUB 5015: GOTO 200: REM H^ ... 'HOME' , IE CLEAR SCRN. 250 IF KY = 18 THEN HOME : GOTO 6010: REM R^...RECONFIGURE 260 IF KY = 16 THEN GOSUB 7010: GOTO 200: REM P^..PRINT SCRN 300 FOR I = 1 TO 10:X = PEEK ( - 16336): NEXT : GOTO 200: REM ...KEYPR ESS ERROR SOUND REM ..... ONERR HANDLER ..... AND 810 X = PEEK (218) + PEEK (219) \* 256:Y = PEEK (222): REM LINE# & ER R CODE 820 PRINT "ERRCODE=":Y:"---LN#=":X 830 GOTO 900 900 POKE 34, 0: POKE 35, 24: END 1000 REM 1001 REM >>>>>> INITIALIZE ((((( 1002 REM 1010 IN\$ = "0":KY = 48:SW = 0:LB = 2:LN = 0: REM INPUT/LABL/LN# VARS POKE - 16368, 0: REM CLEAR KYBD STR \$C010 FOR READKEY. 1015 1020 ABA = 49240:PBA = 49249: REM BASE ADDRS OF ANN & PB. 1030 DIM LAN(3,1), LPB(3), VAN(3), VPB(3): REM LOCATIONS & VALUES. 1040 DIM TITLE\$(3), IHEAD\$(3,3), OHEAD\$(3,3), TEMP\$(7): REM HEADING ARRA YS. 1050 NAN = 3:NPB = 3:BL\$ = " ":DSH\$ = "-": REM # OF COLUMNS & DUMMMY \$'S 1060 DIM SCREEN(23, 38): REM IS USED ALONG WITH V, H & B IN PRINT SCREEN-7000. 1100 FOR I = 0 TO 3: FOR J = 0 TO 1:LAN(I,J) = ABA:ABA = ABA + 1: NEXT J.I

```

1110 FOR I = 0 TO 2:LPB(I) = PBA + I: NEXT I:LPB(3) = 49248: REM CASS.I

N = 4TH PB

1120 FOR I = 0 TO 38:BL$ = BL$ + " ":DSH$ = DSH$ + "-": NEXT I

1130 FOR I = 0 TO 3: READ TITLE$(I)

1140 FOR J = 0 TO 3: READ IHEAD$(I, J):L = LEN (IHEAD$(I, J)):IF L = 2 THEN

IHEAD$(I, J) = " " + IHEAD$(I, J)

IF L = 1 THEN IHEAD(I, J) = " + IHEAD(I, J) + " "

1145

1150

NEXT J: REM ABOVE IS FOR CENTERING/JUSTIFICATION.

1155

FOR J = 0 TO 3: READ OHEAD$(I, J):L = LEN (OHEAD$(I, J)): IF L = 2 THEN

OHEAD$(I, J) = " " + OHEAD$(I, J)

IF L = 1 THEN OHEAD$(I, J) = " " + OHEAD$(I, J) + " "

1160

NEXT J, I

1165

1170

VTAB 24: HTAB 1: INVERSE : PRINT "COMMANDS";: NORMAL

PRINT "...'S'...RTN...H^...R^...P^...Q^...";

1175

1180 POKE 35,23: HOME : RETURN

1200

REM

REM >>>>>> PRINT HEADINGS (((((

1201

1210 FOR I = 0 TO 3: VTAB (I + 1): HTAB 1: CALL - 868: PRINT TITLE$(I)

;":";: REM -868=CLEOL.

FOR J = NAN TO Ø STEP - 1: PRINT " "; IHEAD$(I, J);: NEXT J: PRINT

1230

":";

1240

FOR J = NPB TO Ø STEP - 1: PRINT " ";OHEAD$(I,J);: NEXT J

1250 NEXT I: PRINT : CALL - 868

PRINT LEFT$ (DSH$, (NAN + NPB + 2) * 4 + 7)

1260

VTAB 6: HTAB 1: POKE 34, 5: RETURN

1270

2000

REM

2001

REM >>>> TOGGLE ANNUNCIATOR ((((

2002

REM

2010 VAN(SW) = NOT VAN(SW): REM TOGGLES VALUE

2020

POKE LAN(SW, VAN(SW)), 0: REM SETS LS259

2030

RETURN

3000

REM

3001

REM >>>> READ PUSHBUTTONS ((((

3002

REM

3010 FOR I = 0 TO 2:VPB(I) = PEEK (LPB(I)) > 127: NEXT :VPB(3) =

PEEK

(LPB(3)) ( 128: REM CASSETTE INPUT INVERTS SIGNAL.

3020

RETURN

4000

REM

4001

4002 REM

4010 HTAB (9 + 4 * (NAN - SW)): PRINT VAN(SW) :: REM DISPLAY ONE ANN.

4020 FOR I = NPB TO 0 STEP - 1: REM DISPLAY ALL PB'S.

4030 HTAB (14 + 4 * (NAN + NPB - I)): PRINT VPB(I);: NEXT I

4040 HTAB (8 + 4 * (NAN - TS)): PRINT CHR$ (32);: REM ERASE CURSOR FRO

M LAST POSIT.

4045

HTAB (8 + 4 * (NAN - SW)): FLASH : PRINT CHR$ (32);: NORMAL : REM

PLACE IT AT NEW POSITION (MAY BE UNCHANGED).

4050

RETURN

5000

REM

5001

5002

REM

HTAB (8 + 4 * (NAN - SW)): PRINT CHR$ (32);: REM ERASE CURSOR, REA

5010

D CURRENT LINE POSITION.

5015 X = PEEK (37): REM CURRENT LN#.

5020

IF X ( 21 THEN LN = X - 4

5030

IF X > 20 THEN LN = LN + 1

5040

IF LN > 999 THEN LN = 0

5050

HTAB 40: PRINT : HTAB (3 - (LN ) 9) - (LN ) 99)): PRINT LN;

```

```

5060 FOR I = 0 TO NAN: VAN(I) = 0: POKE LAN(I,0),0: HTAB (9 + 4 * I): PRINT

"0":: NEXT I: PRINT " :";: REM SET ANN'S=0 & PRINT.

5070 SW = 0: GOSUB 3010: GOSUB 4020: REM POSITION CURSOR, READ&DISPLAY PB

15

5080

RETURN

6000

REM

6001

REM >>>>>> RECONFIGURE (((((

6002

RFM

HOME : HTAB 12: PRINT "RECONFIGURATION": HTAB 17: PRINT "MENU": PRINT

6010

PRINT "A... CHANGE # OF COLUMNS"

6020

PRINT "B ... REASSIGN LABELS"

6030

6035

PRINT "C ... RETURN TO MAIN (BREADBOARD)"

6040

PRINT : PRINT : FLASH : PRINT ">>>>>";: NORMAL

6045 GET IN$

IF IN$ = "A" THEN

GOTO 6100

6050

IF IN$ = "B" THEN

6060

GOTO 6200

IF IN$ = "C" THEN HOME : GOSUB 1210: VTAB 5: GOSUB 5015:X = FRE

6065

(0): GOTO 200

6070

FOR I = 1 TO 10:X = PEEK ( - 16336): NEXT : GOTO 6010

REM ..... CHANGE # OF COLUMNS.....

6099

6100 HOME : PRINT "HOW MANY DEVICE INPUTS (#ANN) AND": PRINT "OUTPUT (#

PB) COLUMNS DESIRED?": PRINT : PRINT

6110

INPUT "#ANN(1TO4), #PB(1TO4)";NAN,NPB

IF NAN ( 1 OR NAN ) 4 OR NPB ( 1 OR NPB ) 4 THEN CALL - 1051: CALL

6120

- 1051: GOTO 6100

6130 NAN = NAN - 1:NPB = NPB - 1

GOSUB 1210: GOTO 6010: REM PRINT HEADINGS & RETURN TO RECONFIG. ME

6140

NU.

REM ..... REASSIGN LABELS.....

6199

6200 NAN = 3:NPB = 3: GOSUB 1210: REM FULL WIDTH HEADINGS.

HOME : PRINT : PRINT "REASSIGN LABL1 OR LABL2 (1 OR 2)?": PRINT "(

6210

PRESS SPACE BAR TO RETURN TO MENU)": FLASH : PRINT ">>>>>>":: NORMAL

6230 GET IN$:KY = ASC (IN$) - 48:LB = KY + 1: HOME

IF IN$ = " " THEN GOTO 6010

6235

6240

IF KY ( 1 OR KY ) 2 THEN CALL - 1051: CALL - 1051: HOME : GOTO

6210

INVERSE : PRINT "LABL";KY;: NORMAL : HTAB 7: INPUT ">";IN$

6250

6260 IN$ = "": FOR I = 1671 TO 1702: IN$ = IN$ + CHR$ ( PEEK (I)): NEXT

I: REM

READ LINE 6.

FOR I = 0 TO 7: TEMP$(I) = MID$ (IN$,4 * I + 1 + (I > 3),3): NEXT

6280

6290

HOME : HTAB 7: FOR I = 0 TO 3: PRINT " ";TEMP$(I);: NEXT I: PRINT

":":

6300 FOR I = 4 TO 7: PRINT " ";TEMP$(I);: NEXT I: PRINT : FLASH : PRINT

DSH$: NORMAL : PRINT

PRINT "PRESS (Y)ES TO REASSIGN ABOVE TEXT TO": PRINT "LABL";KY

6310

PRINT "PRESS ANY OTHER KEY TO ABORT THE": PRINT "REASSIGNMENT."

6320

6330 GET IN$: IF IN$ = "Y" THEN GOTO 6400

6340

HOME : VTAB 6: HTAB 8: PRINT "REASSIGNMENT CANCELLED": FOR I = 1 TO

1000: NEXT I: GOTO 6010

FOR I = 0 TO 3: IHEAD$(LB, I) = TEMP$(3 - I): OHEAD$(LB, I) = TEMP$(7 -

6400

I): NEXT I

6410

GOSUB 1210: GOTO 6010: REM PRINT HEADINGS/RETURN TO MENU

7000

REM

7001

REM >>>>>> PRINT SCREEN (((((

7002

REM

```

| 7010 V = PEEK (37) + 1:H = PEEK (36) + 1: REM SAVE CURSOR POSIT.       |

|------------------------------------------------------------------------|

| 7020 FOR I = 1 TO V: VTAB I: CALL - 990:B = PEEK (40) + 256 * PEEK (   |

| 41): FOR $J = \emptyset$ TO 38:SCREEN(I, J) = PEEK (B + J): NEXT J, I  |

| 7030 PRINT CHR\$ (13); CHR\$ (4);"PR#1"                                |

| 7035 PRINT CHR\$ (9);"20L"                                             |

| 7037 PRINT CHR\$ (9);"80N"                                             |

| 7040 FOR I = 1 TO V: FOR J = 0 TO 38: PRINT CHR\$ (SCREEN(I,J));: NEXT |

| J: PRINT : NEXT I                                                      |

| 7050 PRINT CHR\$ (4);"PR# 0"                                           |

| 7060 VTAB V: HTAB H: RETURN                                            |

| 9000 DATA GPSIG, ANO, AN1, AN2, AN3, PB0, PB1, PB2, PB3                |

| 9010 DATA GPIN#, 15, 14, 13, 12, 2, 3, 4, CS                           |

| 9020 DATA LABL1, A, B, C, D, W, X, Y, Z                                |

| 9030 DATA LABL2,0,1,2,3,0,1,2,3                                        |

Listing 2-1. The bulk of the BREADBOARD IN SOFTWARE (BDIS) program is in Applesoft. It is best to type it in exactly as it appears.

| *PR#Ø |    |                 |    | 1  | ******          | **** | ******  | *****                      |

|-------|----|-----------------|----|----|-----------------|------|---------|----------------------------|

| :ASM  |    |                 |    | 2  | *               |      |         | *                          |

|       |    |                 |    | з  | *               | RE   | ADKEY   | *                          |

|       |    |                 |    | 4  | */              | FC   | R BDIS  | *                          |

|       |    |                 |    | 5  | *               |      |         | *                          |

|       |    |                 |    | 6  | ******          | **** | ******* | ******                     |

|       |    |                 |    | 7  |                 |      |         |                            |

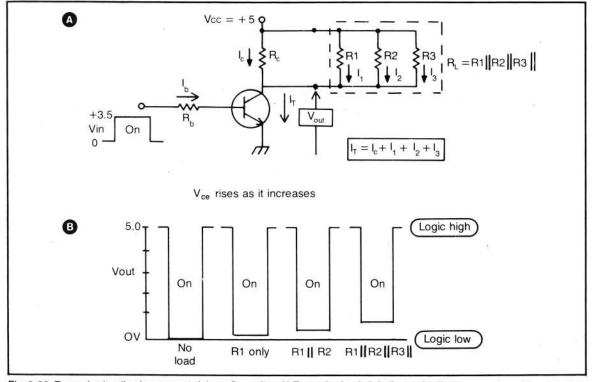

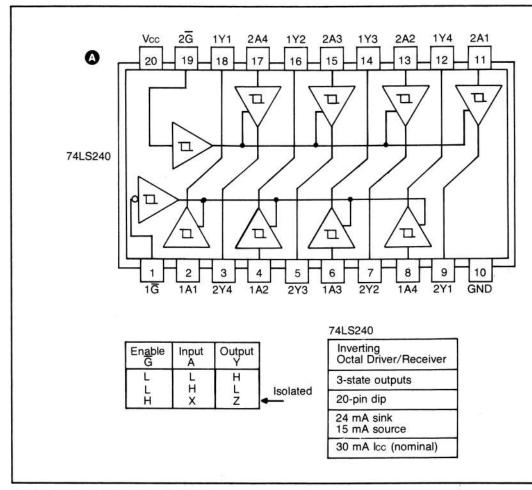

|       |    |                 |    | 8  | KEY             | =    | \$0000  |                            |